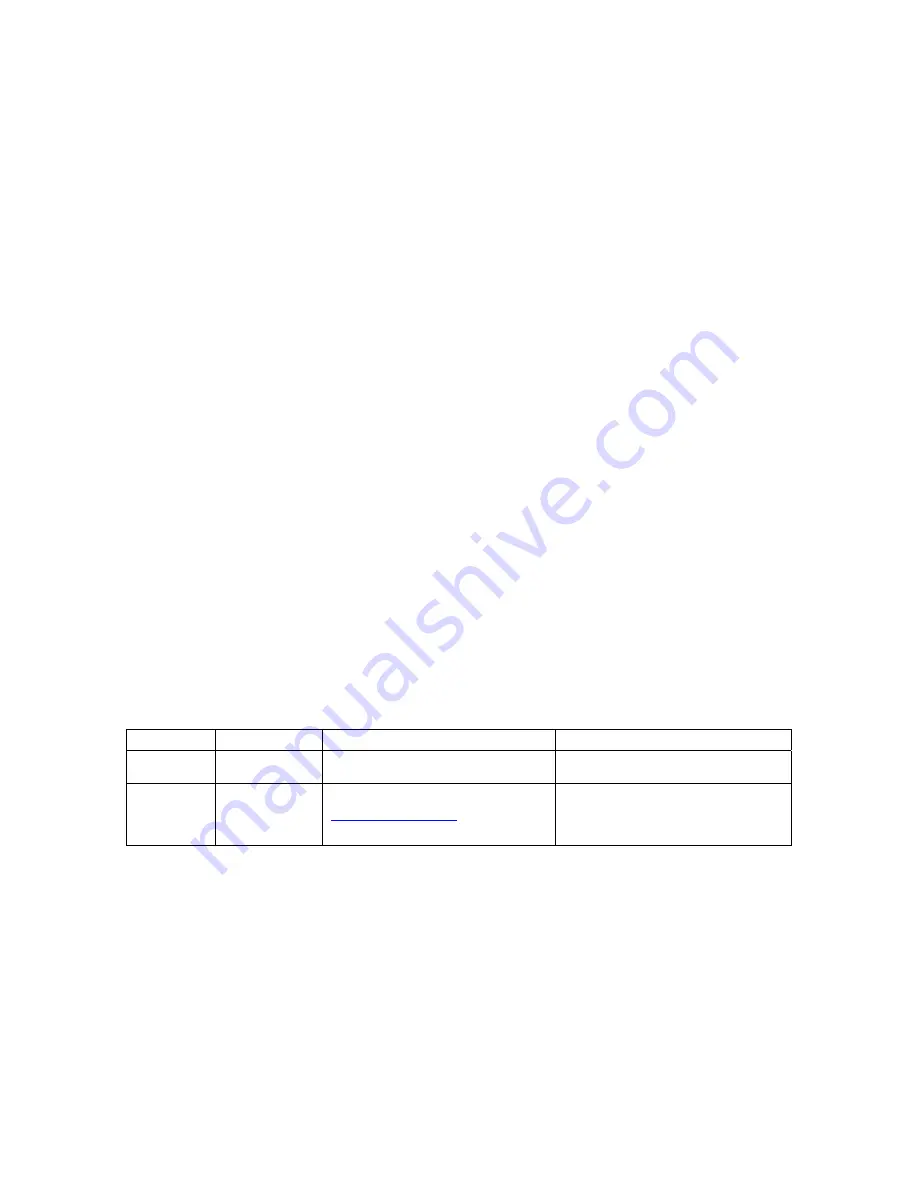

Voyetra Eight Hardware Maintenance Manual

Revision 1.0a

Revision Date

Changed

By

Reason

1.0 ??/??/1984

Carmine

J.

Bonanno Original

Revision

1.0a 06/19/2002

Joan

Touzet

joant@ieee.org

http://www.atypical.net/

Mistake correction

Revisions for clarity

Started schematic entry

“Copywright [

sic

] 1984 by OCTAVE-PLATEAU ELECTRONICS, INC.

51

Main

Street

Yonkers, New York 10701”