Manual PCIe-DIO-24HS PCI Express Digital I/O Card

13

Base Address +2 (read/write) Port C DIO

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

PC7 PC6 PC5 PC4 PC3 PC2 PC1 PC0

Table 5-4:

Base +2 Port C DIO

Reading from this address will return the digital data on Port C. Writing to this address will

output the digital data on Port C. Readback is supported while in output mode. Port C can

also be broken into two nybbles, Port C Low (bits 0-3), and Port C High (bits 4-7). Each nybble

can be independently set as input or output. Base A3 controls Port C's I/O direction.

Base Address +3 (read/write) Control Register

The DIO function contains a control register. This 8-bit register is used to set the direction of

the Ports. At power-up or reset, all DIO lines are automatically set as inputs and should be

configured during initialization by writing to the control register even if the Ports are going to

be used as inputs. Bit 7 must be set to

‘1’ when configuring the direction of the Ports. This

register can be readback with bits 2, 5, 6, and 7 always reading zero.

Ports can be written to while configured as inputs. When a Port is changed from input

to output, the last written value will be applied. If a Port has never been written to, the

value on the Port's pins while in input mode will be applied to the Port when configured

as an output. This prevents the Ports pins from glitching when set as outputs.

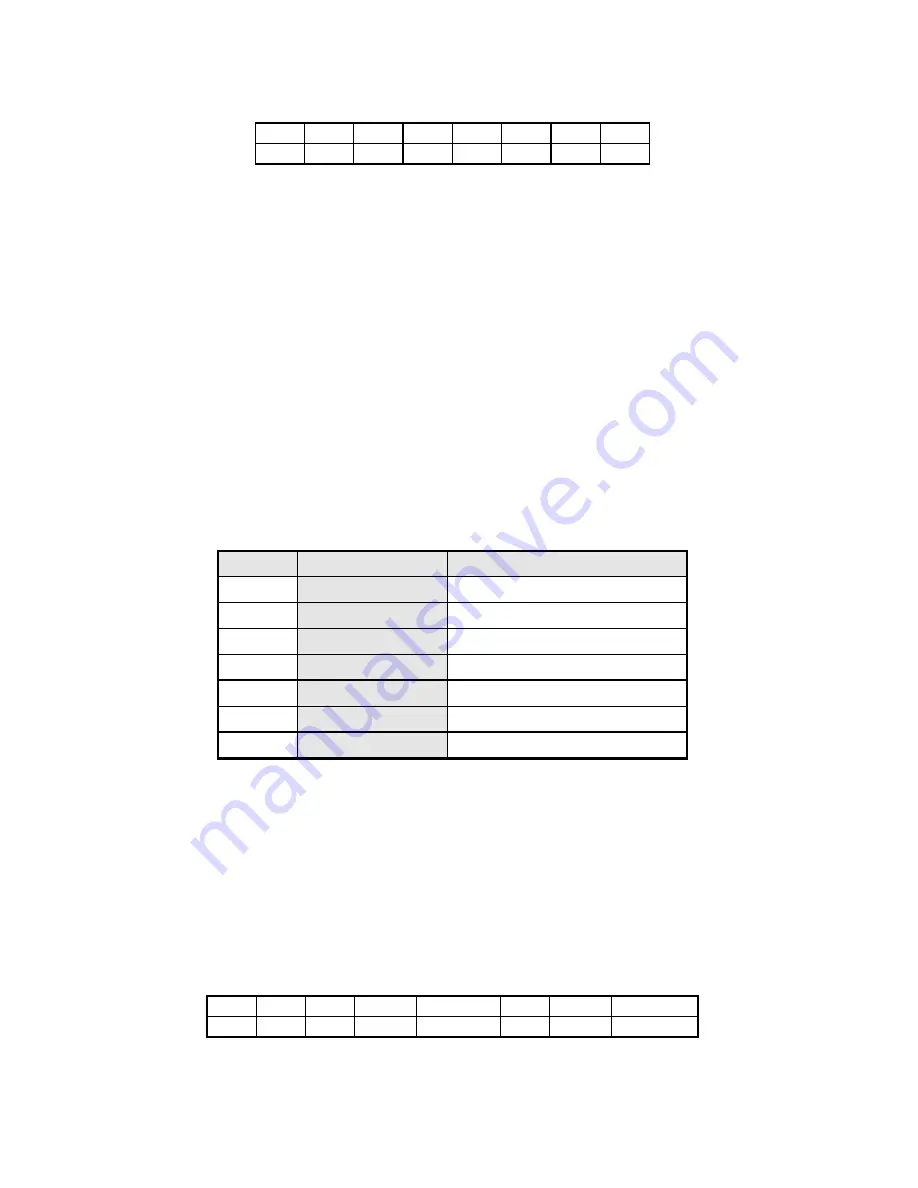

Bit

Assignment

Code

D0

Port C Lo (C0-C3) 1=Input, 0=Output

D1

Port B

1=Input, 0=Output

D2

Reserved

Set to

‘0’

D3

Port C Hi (C4-C7)

1=Input, 0=Output

D4

Port A

1=Input, 0=Output

D5,D6

Reserved

Set to “00”

D7

Direction Set Flag 1=Active

Table 5-5:

Base +3, DIO Port Direction Control Register

Base Address +4 t9 Not Used

Base Address +A (read/write) DIO Buffer Enable / Disable (tri-state)

At power-up or reset, all DIO buffers on the card are enabled. To globally disable the DIO

buffers write a one to bit 0. To globally re-enable the DIO buffers, write a zero to bit 1. When

the buffers are disabled the connector pins are tri-stated and biased by the state of the pull up

or down configuration jumper. A read returns the buffer status; 0=enabled, 1=disabled.

Bit 7 Bit 6 Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

‘0’

‘0’

‘0’

Port A Port C Hi

‘0’

Port B Port C Lo

Table 5-6

: Base +A, DIO Buffer Enable