Multiply Accumulator (Multiplier)

2-26

ADSP-2126x SHARC Processor Hardware Reference

In addition to multiplication, fixed-point operations include accumula-

tion, rounding, and saturation of fixed-point data. There are three

MRF

register operations: clear (

Clr

), round (

Rnd

), and saturate (

Sat

).

The

Clr

operation (

MRF

=0) resets the specified

MRF

register to zero. Often,

it is best to perform this operation at the start of a multiply/accumulate

operation to remove results left over from the previous operation.

The

Rnd

operation (

MRF=Rnd MRF

) applies only to fractional results, so inte-

ger results are not effected. This operation rounds the 80-bit

MRF

value to

nearest at bit 32; for example, the

MRF1

-

MRF0

boundary. Rounding of a

fixed-point result occurs either as part of a multiply or multiply/accumu-

late operation or as an explicit operation on the

MRF

register. The rounded

result in

MRF1

can be sent either to the register file or back to the same

MRF

register. To round a fractional result to zero (truncation) instead of to

nearest, a program transfers the unrounded result from

MRF1

, discarding

the lower 32 bits in

MRF0

.

The

Sat

operation (

MRF=Sat MRF

) sets

MRF

to a maximum value if the

MRF

value has overflowed. Overflow occurs when the

MRF

value is greater than

the maximum value for the data format—unsigned or twos-complement

and integer or fractional—as specified in the saturate instruction. The six

possible maximum values appear in

. The result from

MRF

satura-

tion can be sent either to the register file or back to the same

MRF

register.

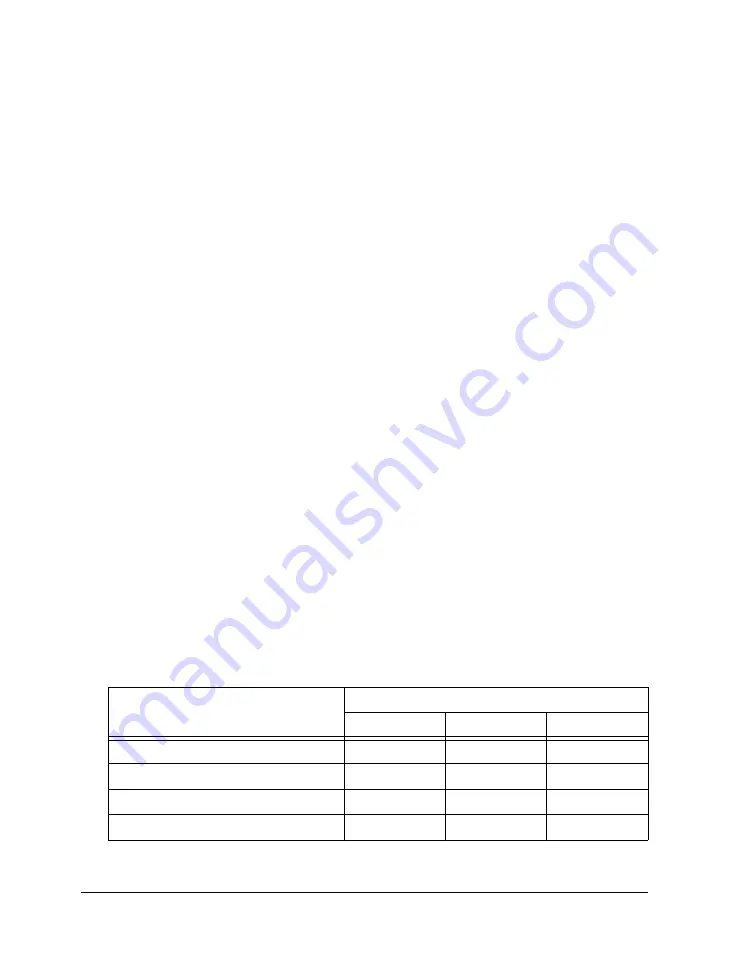

Table 2-6. Fixed-Point Format Maximum Values (For

Saturation)

Maximum Number

(Hexadecimal)

MRF2

MRF1

MRF0

Two’s-complement fractional (positive)

0000

7FFF FFFF

FFFF FFFF

Two’s-complement fractional (negative)

FFFF

8000 0000

0000 0000

Two’s-complement integer (positive)

0000

0000 0000

7FFF FFFF

Two’s-complement integer (negative)

FFFF

FFFF FFFF

8000 0000

Summary of Contents for ADSP-21261 SHARC

Page 30: ...Contents xxx ADSP 2126x SHARC Processor Hardware Reference ...

Page 40: ...Register Diagram Conventions xl ADSP 2126x SHARC Processor Hardware Reference ...

Page 58: ...Differences From Previous SHARCs 1 18 ADSP 2126x SHARC Processor Hardware Reference ...

Page 112: ...Secondary Processing Element PEy 2 54 ADSP 2126x SHARC Processor Hardware Reference ...

Page 178: ...Summary 3 66 ADSP 2126x SHARC Processor Hardware Reference ...

Page 204: ...DAG Instruction Summary 4 26 ADSP 2126x SHARC Processor Hardware Reference ...

Page 322: ...Setting Up DMA 7 32 ADSP 2126x SHARC Processor Hardware Reference ...

Page 436: ...SPORT Programming Examples 9 86 ADSP 2126x SHARC Processor Hardware Reference ...

Page 521: ...ADSP 2126x SHARC Processor Hardware Reference 11 31 Input Data Port rts IDP_ISR end ...

Page 522: ...Input Data Port Programming Example 11 32 ADSP 2126x SHARC Processor Hardware Reference ...

Page 590: ...Timer Programming Examples 14 20 ADSP 2126x SHARC Processor Hardware Reference ...

Page 796: ...I O Processor Registers A 174 ADSP 2126x SHARC Processor Hardware Reference ...

Page 800: ...B 4 ADSP 2126x SHARC Processor Core Manual ...

Page 846: ...Index I 36 ADSP 2126x SHARC Processor Hardware Reference ...