UG-707

ADV8005 Hardware Reference Manual

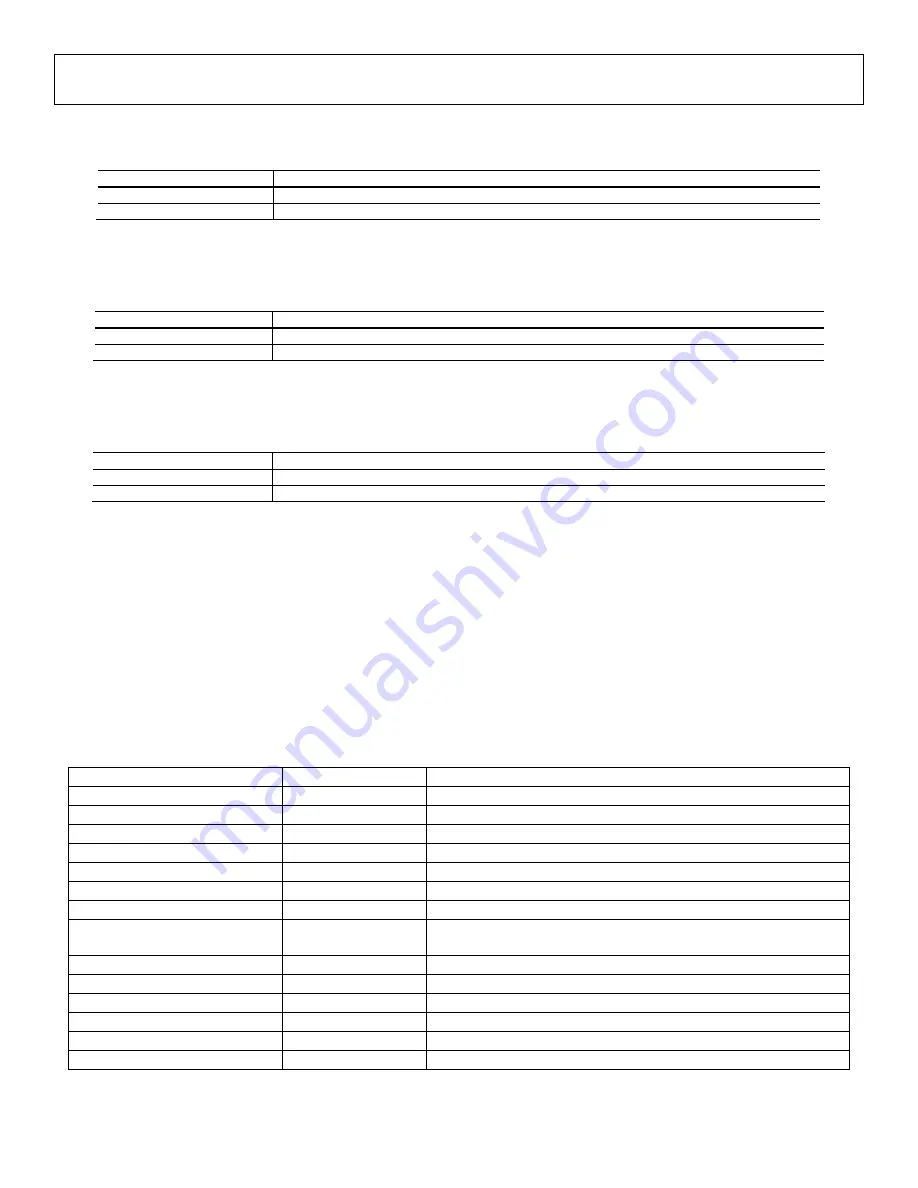

edge_sensitive_int _clr

, IO,

Address 0xXX (Self-Clearing)

This control is used to clear the edge_sensitive_int_raw and edge_sensitive_int_st bits. This is a self clearing bit.

Function

edge_sensitive_int_clr

Description

0

No function

1

Clear edge_sensitive_int_raw and edge_sensitive_int_st

level_sensitive_int_mb2

, IO,

Address 0xXX[0]

This control is used to set the INT2 interrupt mask for the level_sensitive_int interrupt. When set, when the level sensitive interrupt event

triggers and an interrupt is generated on INT2.

Function

level_sensitive_int_mb2

Description

0

Disable level_sensitive_int detection interrupt for INT2

1

Enable level_sensitive_int detection interrupt for INT2

edge_sensitive_int _mb2

, IO,

Address 0xXX

This control is used to set the INT2 interrupt mask for the edge_sensitive_int interrupt. When set, a new edge sensitive interrupt event will

cause edge_sensitive_int_st to be set and an interrupt will be generated on INT2.

Function

edge_sensitive_int_mb2

Description

0

Disable edge_sensitive_int detection interrupt for INT2

1

Enable edge_sensitive_int detection interrupt for INT2

In this section, all raw bits are classified as being triggered by either level-sensitive or edge-sensitive events, with the following understanding of

the terminology.

Level-sensitive events are events that are generally either high or low and which are not expected to change rapidly. The raw bit for level-sensitive

events is not latched and, therefore, always represents the true real-time status of the event in question.

Edge-sensitive events are events that only exist for an instant. The raw bits for edge-sensitive events are latched and, therefore, represent the

occurrence of an edge-sensitive event that happened in the past. Raw bits for edge-sensitive events must be cleared by the corresponding clear

bit.

8.2.2.

Interrupt Architecture Overview

The following is a complete list of Serial Video Rx interrupts, their mode of operation (edge or level sensitive) and a description of each interrupt.

Table 84: Serial Video Rx Level Sensitive Interrupts

Interrupt

Mode of Operation

Description

rx_cable_det_raw/st/mb1/clr

Level sensitive

Used to detect if the Serial Video inputs are connected to an upstream IC

rx_tmdspll_lck_raw/st/mbx/clr

Level sensitive

Used to indicate if the TMDS PLL has locked to the incoming TMDS clock

rx_tmds_clk_det_raw/st/mbx/clr

Level sensitive

Used to indicate activity on the TMDS clock line

rx_video_3d_raw/st/mbx/clr

Level sensitive

Used to indicate if the incoming video is 3D format

rx_av_mute_raw/st/mbx/clr

Level sensitive

Used to indicate the AVMUTE value from the general control packet

rx_hdmi_mode_raw/st/mbx/clr

Level sensitive

Used to indicate if the incoming video is HDMI mode or DVI mode

rx_gen_ctl_pckt_raw/st/mbx/clr

Level sensitive

Used to indicate if a general control packet has been detected

rx_gamut_mdata_

pckt_raw/st/mbx/clr

Level sensitive

Used to indicate if a gamut metadata packet has been detected

rx_isrc2_pckt_raw/st/mbx/clr

Level sensitive

Used to indicate if an ISRC2 packet has been detected

rx_isrc1_pckt_raw/st/mbx/clr

Level sensitive

Used to indicate if an ISRC1 packet has been detected

rx_vs_info_frm_raw/st/mbx/clr

Level sensitive

Used to indicate if a vendor specific InfoFrame has been detected

rx_ms_info_frm_raw/st/mbx/clr

Level sensitive

Used to indicate if an MPEG source InfoFrame has been detected

rx_spd_info_frm_ raw/st/mbx/clr

Level sensitive

Used to indicate if an SPD InfoFrame has been detected

rx_avi_info_frm_raw/st/mbx/clr

Level sensitive

Used to indicate if an AVI InfoFrame has been detected

Rev. A | Page 284 of 317