Exercise 1, Part 2: Analyzing Performance and Memory

Hierarchy Impact

1-14

Getting Started with ADSP-BF537 EZ-KIT Lite

The Blackfin processor has a memory hierarchy with a small amount of

internal SRAM (L1) flexible in its configuration. You can configure the

SRAM as a cache for slower external SDRAM or as “straight” memory for

completely optimal, zero latency, access speed. The fact is, the

Sorts_1_2.dpj

program currently is running under somewhat artificial

“worse case” conditions. The program’s code has been placed into external

SDRAM, while internal memory of the Blackfin processor remains com-

pletely unused.

The next steps demonstrate how the proper utilization of the memory

hierarchy of the Blackfin processor can improve dramatically the program

performance. The “easiest” way to improve the performance is to enable

the instruction cache

1

of the Blackfin processor.

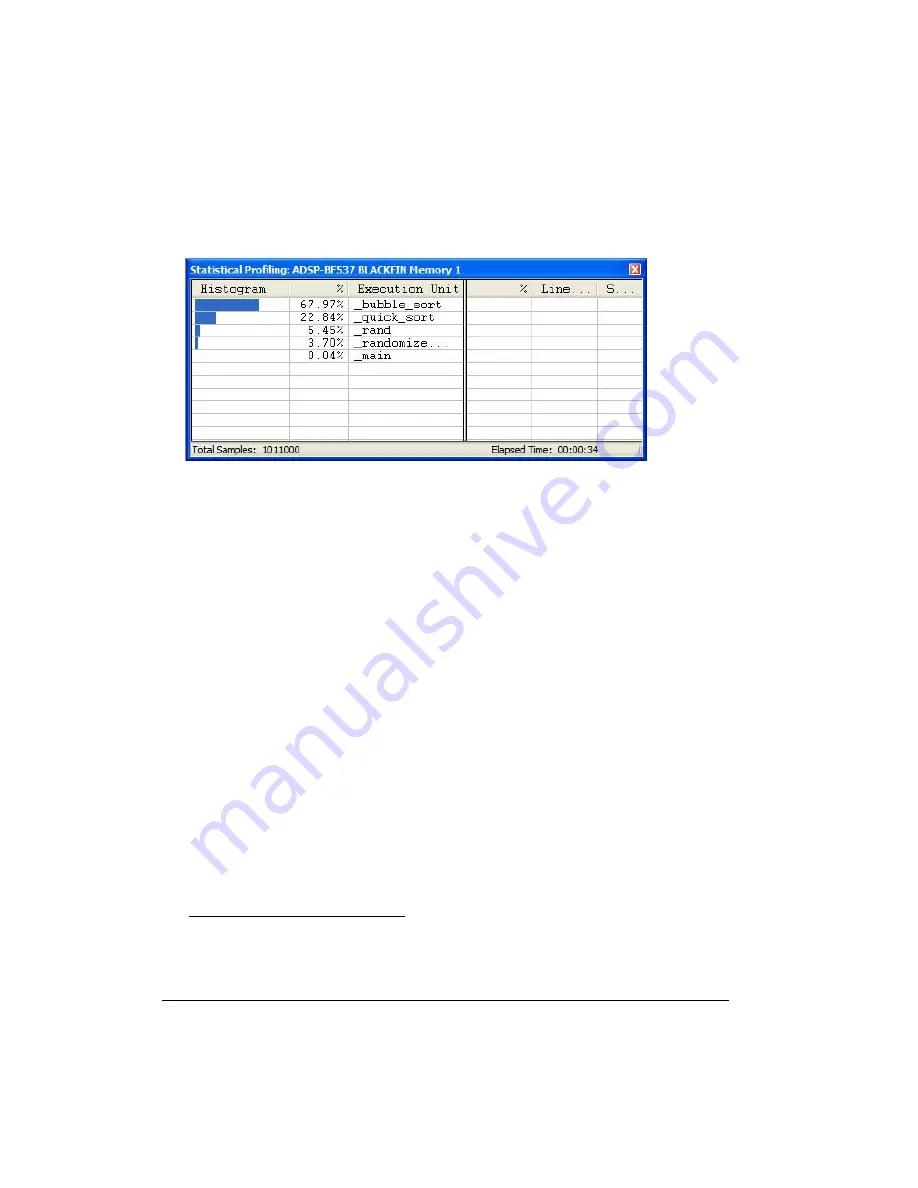

Figure 1-7. Statistical Profiling: Initial Results

1

The Blackfin processor also has a data cache, but its discussion is beyond this exercise. Refer to the

ADSP-BF537 Blackfin Processor Hardware Reference

for more information.

www.BDTIC.com/ADI