Coprocessor Interface

7-4

Copyright © ARM Limited 2000. All rights reserved.

7.2

LDC/STC

The

LDC

and

STC

instructions are used respectively to transfer data to and from external

coprocessor registers and memory. For the ARM946E-S, the memory can be either

internal memory (cache or tightly-coupled memory) or AHB depending on the address

range of the access and the protection unit settings.

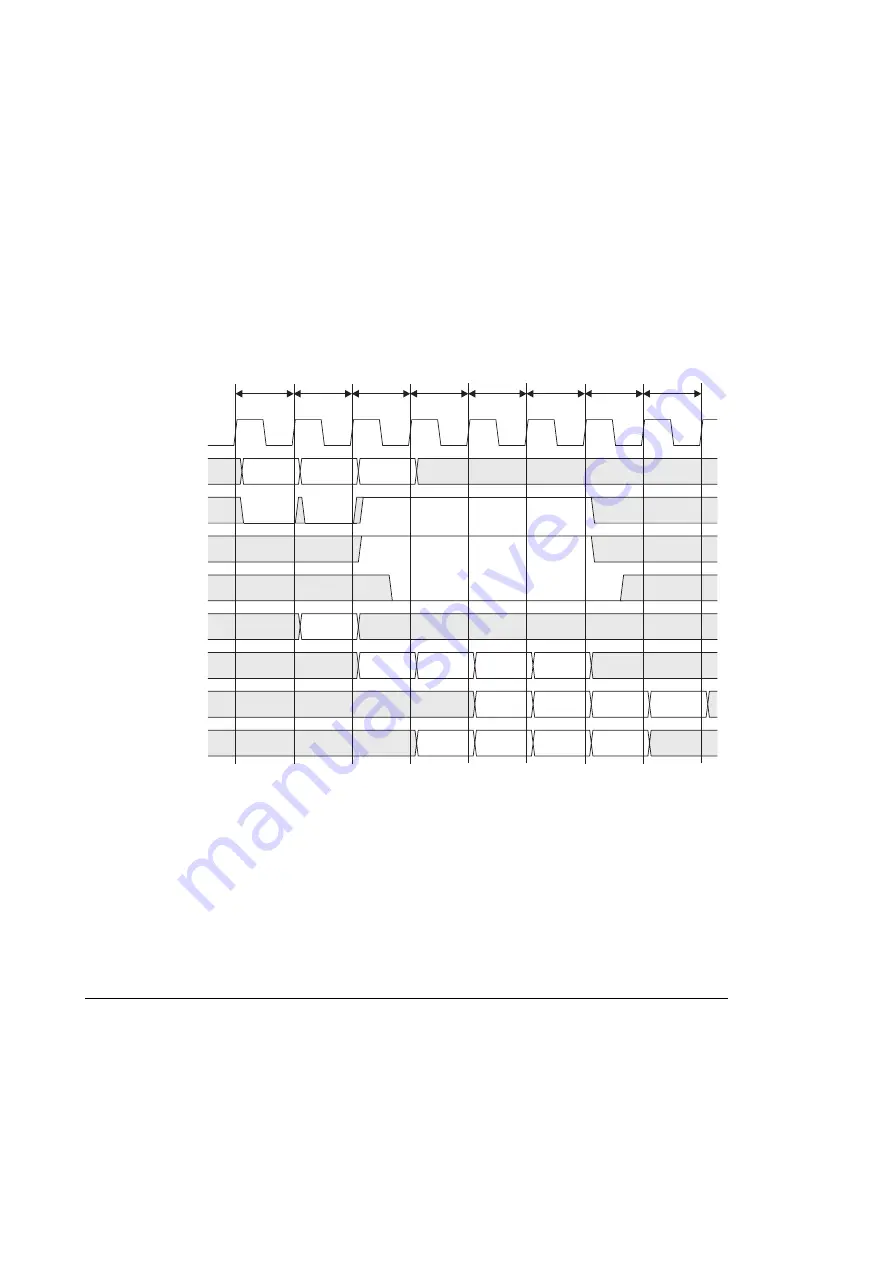

The cycle timing for these operations is shown in Figure 7-2.

Figure 7-2 LDC/STC cycle timing

In this example, four words of data are transferred. The number of words transferred is

determined by how the coprocessor drives the CHSDE[1:0] and CHSEX[1:0] buses.

As with all other instructions, the ARM9E-S performs the main Decode off the rising

edge of the clock during the Decode stage. From this, the core commits to executing the

instruction and so performs an instruction Fetch. The coprocessor instruction pipeline

keeps in step with ARM9E-S core by monitoring nCPMREQ. This is a registered

version of the ARM9E-S core instruction memory request signal InMREQ.

GO

GO

LAST

Ignored

GO

CLK

nCPMREQ

CPINSTR[31:0]

CHSDE[1:0]

CHSEX[1:0]

CPDOUT[31:0]

LDC

CPPASS

CPLATECANCEL

LDC

CPDIN[31:0]

STC

Decode

Execute

(GO)

Execute

(GO)

Execute

(GO)

Execute

(LAST)

Memory

Write

Coprocessor

pipeline

Fetch

Summary of Contents for ARM946E-S

Page 1: ...ARM DDI 0155A ARM946E S Technical Reference Manual ...

Page 6: ...vi Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A 04 Limited Confidential ...

Page 54: ...Programmer s Model 2 34 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...

Page 70: ...Caches 3 16 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...

Page 78: ...Protection Unit 4 8 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...

Page 112: ...Coprocessor Interface 7 14 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...