Coprocessor Interface

7-12

Copyright © ARM Limited 2000. All rights reserved.

7.6

Privileged instructions

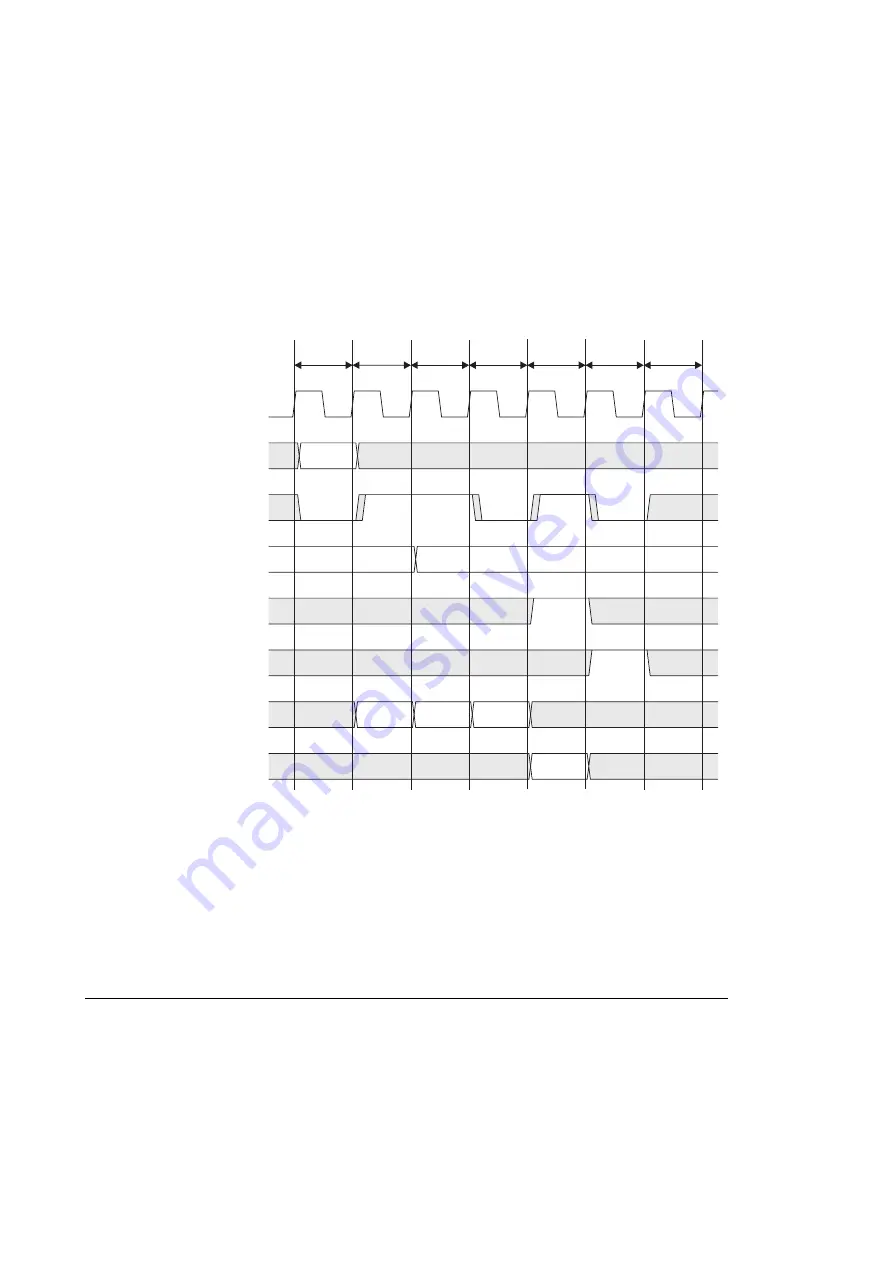

The coprocessor can restrict certain instructions for use in privileged modes only. To do

this, the coprocessor tracks the nCPTRANS output. Figure 7-6 shows how

nCPTRANS changes after a mode change.

Figure 7-6 Privileged instructions

The first two CHSDE[1:0] responses are ignored by the ARM9E-S because it is only

the final CHSDE[1:0] response, as the instruction moves from Decode into Execute,

that counts. This allows the coprocessor to change its response as nCPTRANS

changes.

Ignored

Ignored

CLK

nCPMREQ

CPINSTR[31:0]

CHSDE[1:0]

CHSEX[1:0]

CPPASS

CPLATECANCEL

CPRT

Decode

Decode

Decode

Execute

Memory

Coprocessor

pipeline

Ignored

Instruction

aborted

nCPTRANS

Old mode

New mode

LAST

Fetch

Summary of Contents for ARM946E-S

Page 1: ...ARM DDI 0155A ARM946E S Technical Reference Manual ...

Page 6: ...vi Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A 04 Limited Confidential ...

Page 54: ...Programmer s Model 2 34 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...

Page 70: ...Caches 3 16 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...

Page 78: ...Protection Unit 4 8 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...

Page 112: ...Coprocessor Interface 7 14 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...