Coprocessor Interface

Copyright © ARM Limited 2000. All rights reserved.

7-13

7.7

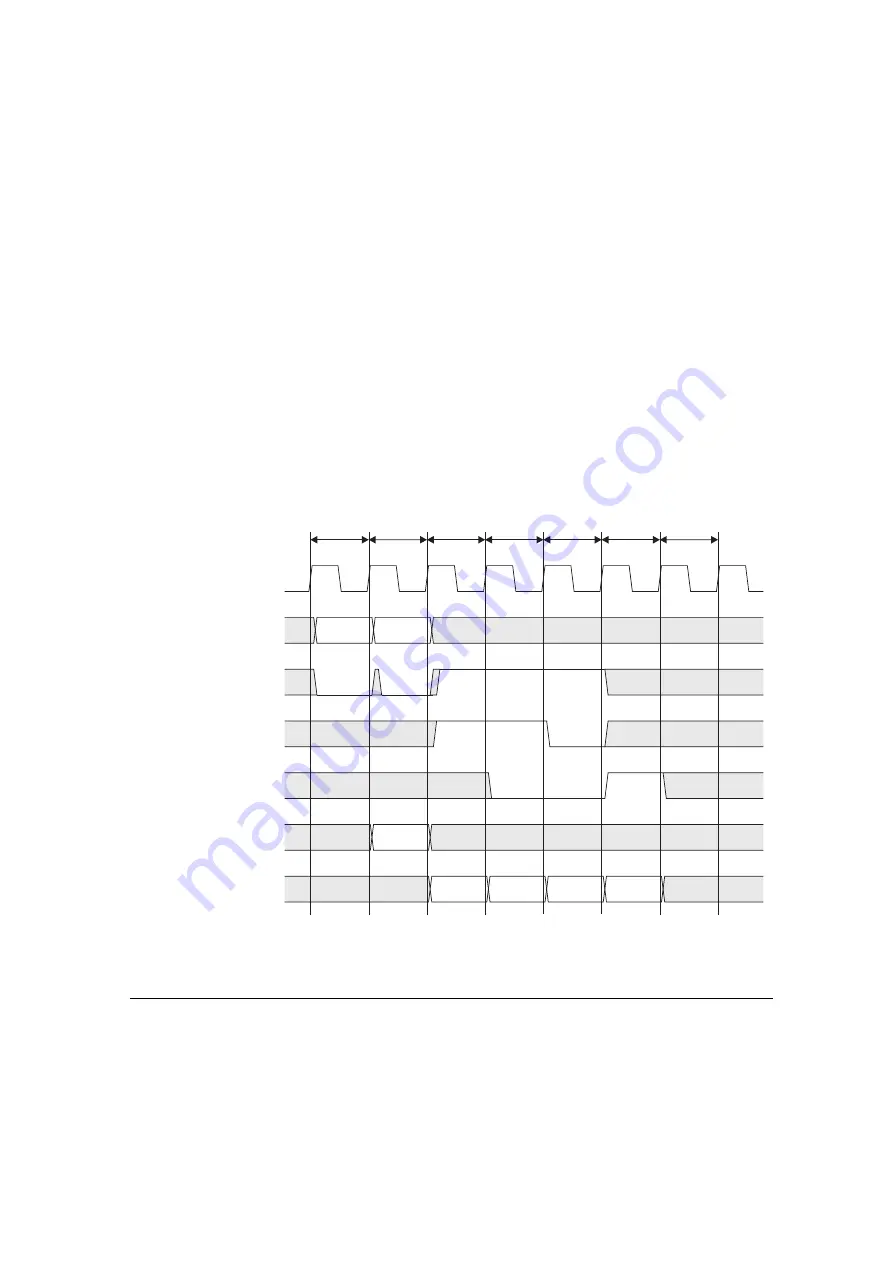

Busy-waiting and interrupts

The coprocessor is permitted to stall, or busy-wait, the processor during the execution

of a coprocessor instruction if, for example, it is still busy with an earlier coprocessor

instruction. To do so, the coprocessor associated with the Decode stage instruction

drives WAIT onto CHSDE[1:0]. When the instruction concerned enters the Execute

stage of the pipeline, the coprocessor can drive WAIT onto CHSEX[1:0] for as many

cycles as necessary to keep the instruction in the busy-wait loop.

For interrupt latency reasons the coprocessor can be interrupted while busy-waiting.

This causes the instruction to be abandoned. Abandoning execution is done through

CPPASS. The coprocessor must monitor the state of CPPASS during every busy-wait

cycle. If it is HIGH, the instruction must still be executed. If it is LOW, the instruction

must be abandoned.

Figure 7-7 shows a busy-waited coprocessor instruction abandoned due to an interrupt.

CPLATECANCEL is also asserted as a result of the Execute interruption.

Figure 7-7 Busy-waiting and interrupts

WAIT

WAIT

WAIT

CLK

nCPMREQ

CPINSTR[31:0]

CHSDE[1:0]

CHSEX[1:0]

CPPASS

CPLATECANCEL

CPInstr

Decode

Execute

(WAIT)

Execute

(WAIT)

Execute

(WAIT)

Execute

(WAIT)

Coprocessor

pipeline

WAIT

Ignored

Execute

interrupted

Fetch

Summary of Contents for ARM946E-S

Page 1: ...ARM DDI 0155A ARM946E S Technical Reference Manual ...

Page 6: ...vi Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A 04 Limited Confidential ...

Page 54: ...Programmer s Model 2 34 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...

Page 70: ...Caches 3 16 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...

Page 78: ...Protection Unit 4 8 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...

Page 112: ...Coprocessor Interface 7 14 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...