Debug Support

ARM DDI 0186A

Copyright © 2000 ARM Limited. All rights reserved.

8-11

8.4.3

Watchpoints

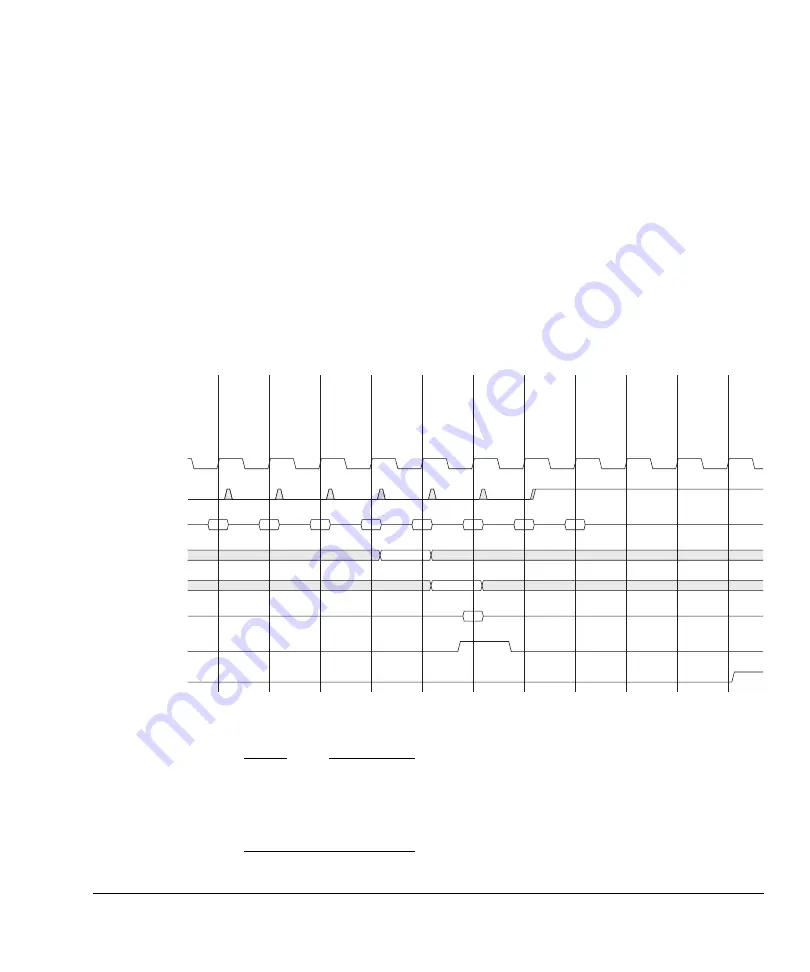

Entry into debug state following a watchpointed memory access is imprecise. This is

necessary because of the nature of the pipeline.

External logic, such as external watchpoint comparators, can be built to extend the

functionality of the EmbeddedICE-RT logic. Their output must be applied to the

DBGDEWPT

input. This signal is simply ORed with the internally-generated

Watchpoint

signal before being applied to the ARM9E-S core control logic. The timing

of the input makes it unlikely that data-dependent external watchpoints are possible.

After a watchpointed access, the next instruction in the processor pipeline is always

allowed to complete execution. Where this instruction is a single-cycle data-processing

instruction, entry into debug state is delayed for one cycle while the instruction

completes. The timing of debug entry following a watchpointed load in this case is

shown in Figure 8-5.

Figure 8-5 Watchpoint entry with data processing instruction

Note

Although instruction 5 enters the Execute stage, it is not executed, and there is no state

update as a result of this instruction. When the debugging session is complete, normal

continuation involves a return to instruction 5, the next instruction in the code sequence

to be executed.

CLK

NSTR[31:0]

InMREQ

RDATA[31:0]

1

M1

E1

W1

D1

WDATA[31:0]

DA[31:0]

2

LDR

Dp

5

6

F1

M2

E2

W2

D2

F2

Mldr

Eldr

Wldr

Dldr

Fldr

MDp

EDp

WDp

DDp

FDp

M5

E5

W5

D5

F5

Edebug1

Ddebug

Edebug2

7

8

DBGDEWPT

DBGACK

Summary of Contents for ARM966E-S

Page 6: ...Contents vi Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 20: ...Introduction 1 4 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 48: ...Tightly coupled SRAM 4 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 80: ...Bus Interface Unit 6 20 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 118: ...Debug Support 8 26 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 130: ...Test Support 10 8 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 142: ...Instruction cycle timings 11 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 158: ...Signal Descriptions A 16 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 176: ...AC Parameters B 18 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...