Test Support

10-6

Copyright © 2000 ARM Limited. All rights reserved.

ARM DDI 0186A

10.3.3

Pause modes

The suggested production test sequence for the SRAM is:

1.

Test each SRAM using a full test.

2.

Test the BIST hardware for each SRAM. To allow testing of the BIST hardware,

a pause mechanism enables the BIST test to be halted and data within the SRAM

to be corrupted. The sequence for this is:

a.

Writing the address for the location to be corrupted with a

MCR

to the

relevant BIST address register.

b.

Writing the corrupted data using a

MCR

to the BIST general register.

c.

Restarting the test by an

MCR

to the BIST control register.

d.

Checking that the corrupted data causes the test to fail by reading the failed

address and data from the BIST address and general registers.

In addition to controlling the addressing within the address and general registers, the

pause bit also controls the progression of the BIST algorithm as follows:

•

•

Auto pause

If the pause bit is set in the BIST control register before the test is activated, the test runs

in auto pause mode. The BIST test pauses at predetermined points of the BIST

algorithm, for instance when the algorithm has reached the top or the bottom of the

memory array being tested.

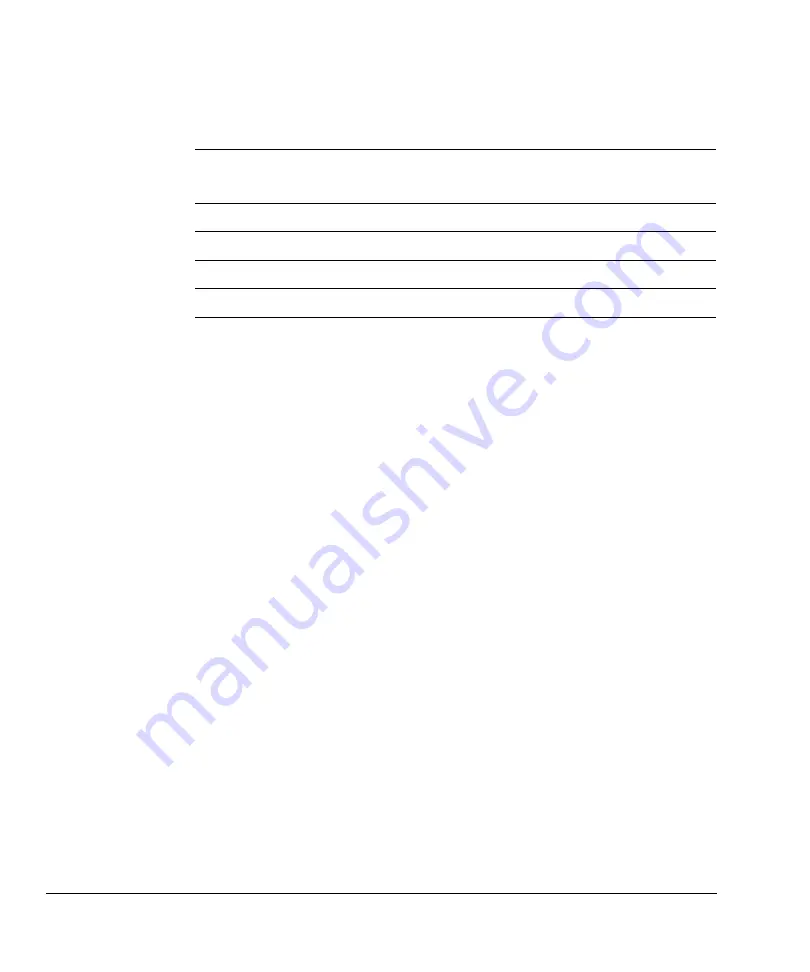

Table 10-2 Data BIST address and general registers

BIST register

IBIST

pause

Read

Write

DBIST address register

0

DBIST fail address

DBIST start address

DBIST address register

1

DBIST fail address

DBIST peek/poke address

DBIST general register

0

DBIST fail data

DBIST seed data

DBIST general register

1

DBIST peek data

DBIST poke data

Summary of Contents for ARM966E-S

Page 6: ...Contents vi Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 20: ...Introduction 1 4 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 48: ...Tightly coupled SRAM 4 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 80: ...Bus Interface Unit 6 20 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 118: ...Debug Support 8 26 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 130: ...Test Support 10 8 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 142: ...Instruction cycle timings 11 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 158: ...Signal Descriptions A 16 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 176: ...AC Parameters B 18 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...