SRAM Stall Cycles

C-2

Copyright © 2000 ARM Limited. All rights reserved.

ARM DDI 0186A

C.1

About SRAM stall cycles

Stall cycles can occur in both the instruction and data SRAMs, with one stall

mechanism being shared between the SRAMs and additional stall mechanism attributed

to the I-SRAM only. Any stall requirement is detected by the SRAM control and

factored into its response to the ARM966E-S system controller. The ARM9E-S

SYSCLKEN

input is then deasserted until the SRAM has performed the access.

C.1.1

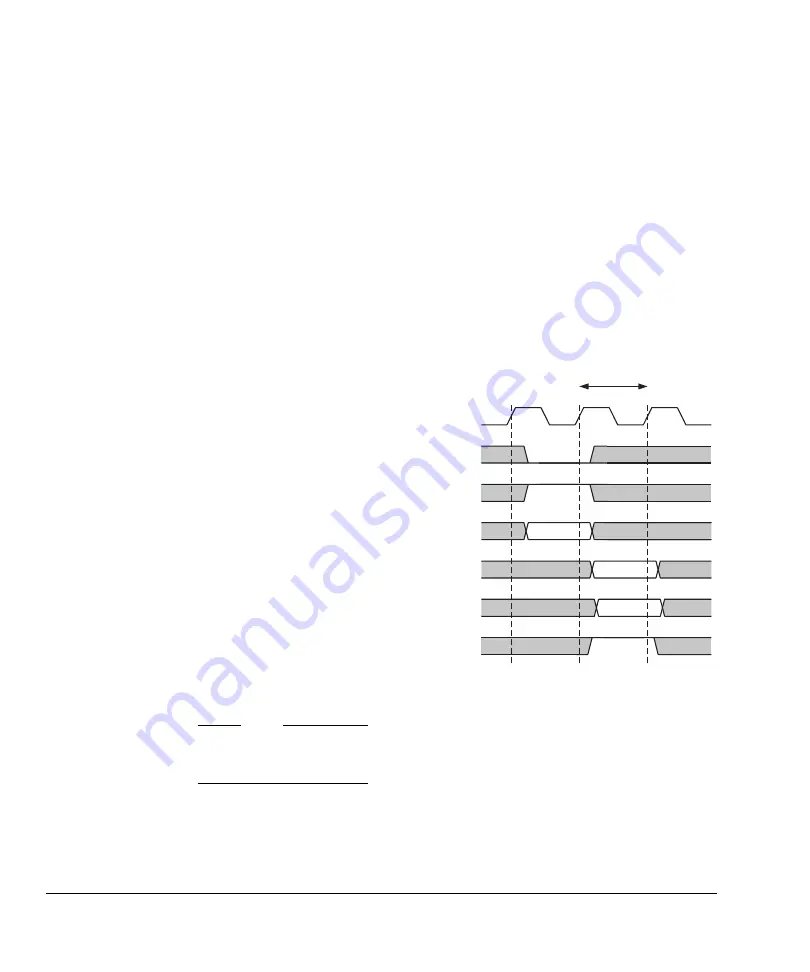

Read-follows-write

This stall mechanism is shared by both instruction and data SRAM because of the

pipelined nature of write data from the ARM9E-S core. The write data appears on the

core interface in the cycle after the address, so that it is not possible to perform the write

until the next rising clock edge. The address from the core must therefore be pipelined

to line up with the write data. A write with pipelined address is shown in Figure C-1.

Figure C-1 SRAM write cycle

Note

The write is performed on the second rising edge of the period marked D-SRAM write

cycle.

In the case of back-to-back writes, stalls do not occur because the pipelined address is

being used and this keeps in step with the data. However, if a read follows the write, the

write must first be allowed to complete before the lookup for the read can be performed.

Write data

Addr A (write)

Addr A

CLK

DnMREQ

DnRW

DA[31:1]

SRAM Addr

WDATA[31:0]

WEN

D-SRAM write

cycle

Summary of Contents for ARM966E-S

Page 6: ...Contents vi Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 20: ...Introduction 1 4 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 48: ...Tightly coupled SRAM 4 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 80: ...Bus Interface Unit 6 20 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 118: ...Debug Support 8 26 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 130: ...Test Support 10 8 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 142: ...Instruction cycle timings 11 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 158: ...Signal Descriptions A 16 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 176: ...AC Parameters B 18 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...