Memory Map

ARM DDI 0186A

Copyright © 2000 ARM Limited. All rights reserved.

3-3

3.2

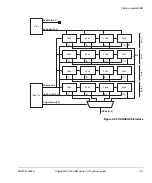

Tightly-coupled SRAM address space

The tightly-coupled

Instruction SRAM

(I-SRAM) and

Data SRAM

(D-SRAM) are

located at the bottom of the memory map. Each SRAM is allocated a 64MB address

space, the bottom 64MB space mapping to I-SRAM and the next 64MB range mapping

to D-SRAM.

In practice, each SRAM is likely to be much smaller than the 64MB allowable and the

address decode is implemented so that each memory is aliased throughout its 64MB

range. See Figure 3-2 for an example of a 16KB I-SRAM aliased through the 64MB

address space.

Figure 3-2 I-SRAM aliasing example

All accesses to addresses above the 128MB combined SRAM address space result in

AMBA AHB transfers controlled by the

Bus Interface Unit

(BIU).

An instruction fetch from the ARM9E-S core to the D-SRAM address space goes to the

AHB, regardless of whether the D-SRAM is enabled. A data interface access from the

ARM9E-S core can access both the D-SRAM

and

the I-SRAM. The ability to

additionally access the I-SRAM is required to allow the fetching of inline literals within

code, for programming of the instruction I-SRAM, and for debugging purposes.

When an SRAM is disabled, all accesses to its address space go to the AHB. When

enabled, the SRAM must be programmed before use. The tightly-coupled SRAMs can

be enabled or disabled during reset depending on the value of the input pin

INITRAM

.

Several boot options are available using

INITRAM

and the exception vectors location

pin

VINITHI

. These are discussed in

D-SRAM space

I-SRAM alias #1

I-SRAM (16KB)

0x0400 0000

0x03FF FFFF

0x03FF C000

0x0000 BFFF

0x0000 8000

0x0000 7FFF

0x0000 4000

0x0000 3FFF

0x0000 0000

I-SRAM alias #2

I-SRAM alias #4095

Summary of Contents for ARM966E-S

Page 6: ...Contents vi Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 20: ...Introduction 1 4 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 48: ...Tightly coupled SRAM 4 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 80: ...Bus Interface Unit 6 20 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 118: ...Debug Support 8 26 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 130: ...Test Support 10 8 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 142: ...Instruction cycle timings 11 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 158: ...Signal Descriptions A 16 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 176: ...AC Parameters B 18 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...