Bus Interface Unit

6-8

Copyright © 2000 ARM Limited. All rights reserved.

ARM DDI 0186A

Burst transfers

Because the ARM966E-S does not implement cache memory, burst transfers of fixed

length commonly used for cache linefill and data cache writeback, are not supported.

All burst accesses are defined to be INCRemental (

HBURST[2:0]

= 001), because the

only indication to the ARM966E-S about the sequentiality of the access is the

DMORE

output from the ARM9E-S core. This output indicates that there is at least one more

access following the current access, but does not indicate how many more sequential

accesses can be expected.

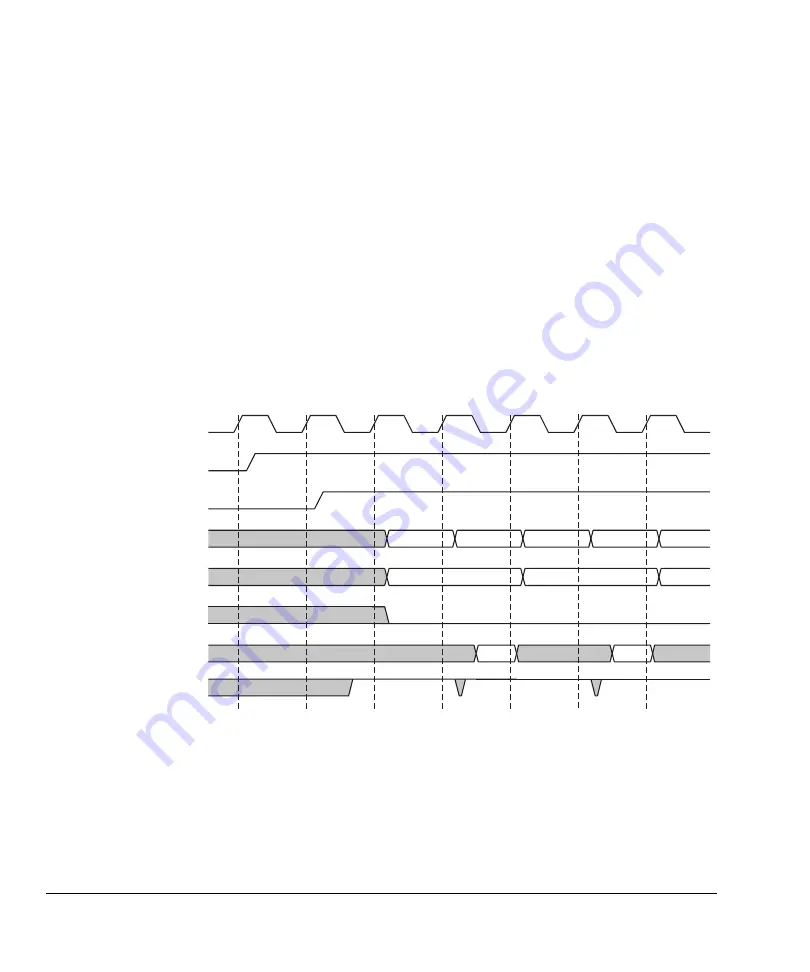

Bus request

At the start of every AHB access, the ARM966E-S requests access to the bus by

asserting

HBUSREQ

to the arbiter. It must then wait for an acknowledge signal from

the arbiter (

HGRANT

), before beginning the transfer on the next rising edge of

HCLK

.

In Figure 6-2, the slave being addressed has a single-cycle response to the read access

and therefore the

HREADY

response is driven HIGH and fed to the ARM966E-S BIU.

Figure 6-2 Sequential instruction fetches, after being granted the bus

Sequential instruction fetch

When the ARM9E-S fetches instructions from the AHB address space or if the

tightly-coupled I-SRAM is disabled, AHB read transfers are initiated by the BIU. The

instruction interface does not have the benefit of a pipelined

MORE

signal, so the BIU

CLK

HTRANS

NONSEQ

IDLE

NONSEQ

IDLE

NONSEQ

HADDR

IA-1

HBUSREQ

HGRANT

HWRITE

HREADY

HRDATA

ID-1

ID-2

IA-2

Summary of Contents for ARM966E-S

Page 6: ...Contents vi Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 20: ...Introduction 1 4 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 48: ...Tightly coupled SRAM 4 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 80: ...Bus Interface Unit 6 20 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 118: ...Debug Support 8 26 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 130: ...Test Support 10 8 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 142: ...Instruction cycle timings 11 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 158: ...Signal Descriptions A 16 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 176: ...AC Parameters B 18 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...