Bus Interface Unit

ARM DDI 0186A

Copyright © 2000 ARM Limited. All rights reserved.

6-11

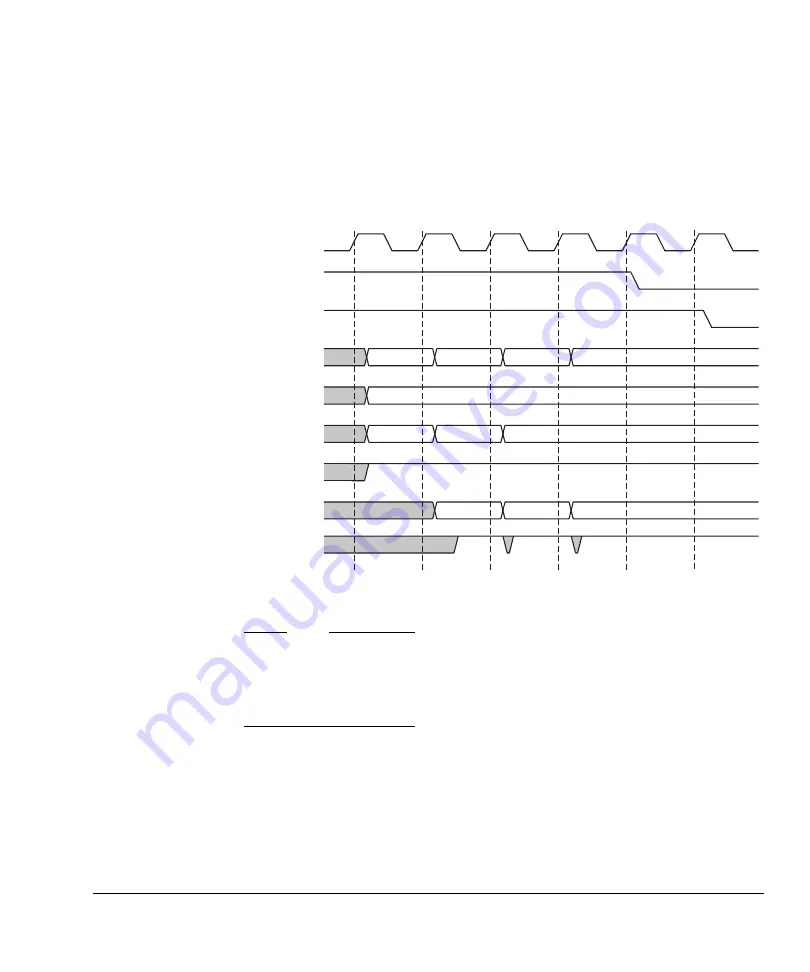

STM timing

Figure 6-6 shows the timing for an

STM

instruction, transferring three words. Outputs to

the AHB are not driven during IDLE cycles, and so hold their previous value. This

includes the

HBURST

output, continuing to indicate INCRemental until the next

nonsequential transfer. This should not cause any confusion to other AHB components

as

HTRANS

indicates IDLE cycles.

Figure 6-6 Single STM, no instruction fetch

Note

If an

STM

is not immediately followed by an external instruction access one IDLE cycle

is inserted, and

HBUSREQ

is driven LOW. An

STM

, immediately followed by any other

AHB data access, also results in one IDLE cycle being inserted between the two

accesses.

LDM timing

Figure 6-7 on page 6-12 shows the timing for an

LDM

instruction, transferring three

words.

HGRANT

HTRANS

SEQ

HBURST

NONSEQ

SEQ

IDLE

001

CLK

HBUSREQ

HWRITE

HREADY

HWDATA

HADDR

DA-1

DA-2

DA-3

DD-1

DD-2

DD-3

Summary of Contents for ARM966E-S

Page 6: ...Contents vi Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 20: ...Introduction 1 4 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 48: ...Tightly coupled SRAM 4 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 80: ...Bus Interface Unit 6 20 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 118: ...Debug Support 8 26 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 130: ...Test Support 10 8 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 142: ...Instruction cycle timings 11 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 158: ...Signal Descriptions A 16 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 176: ...AC Parameters B 18 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...