C11.35 ID Register 3

The TRCIDR3 characteristics are:

Purpose

Indicates:

• Whether TRCVICTLR is supported.

• The number of cores available for tracing.

• If an exception level supports instruction tracing.

• The minimum threshold value for instruction trace cycle counting.

• Whether the synchronization period is fixed.

• Whether TRCSTALLCTLR is supported and if so whether it supports trace overflow

prevention and supports stall control of the processor.

Usage constraints

There are no usage constraints.

Configurations

Available in all configurations.

Attributes

See

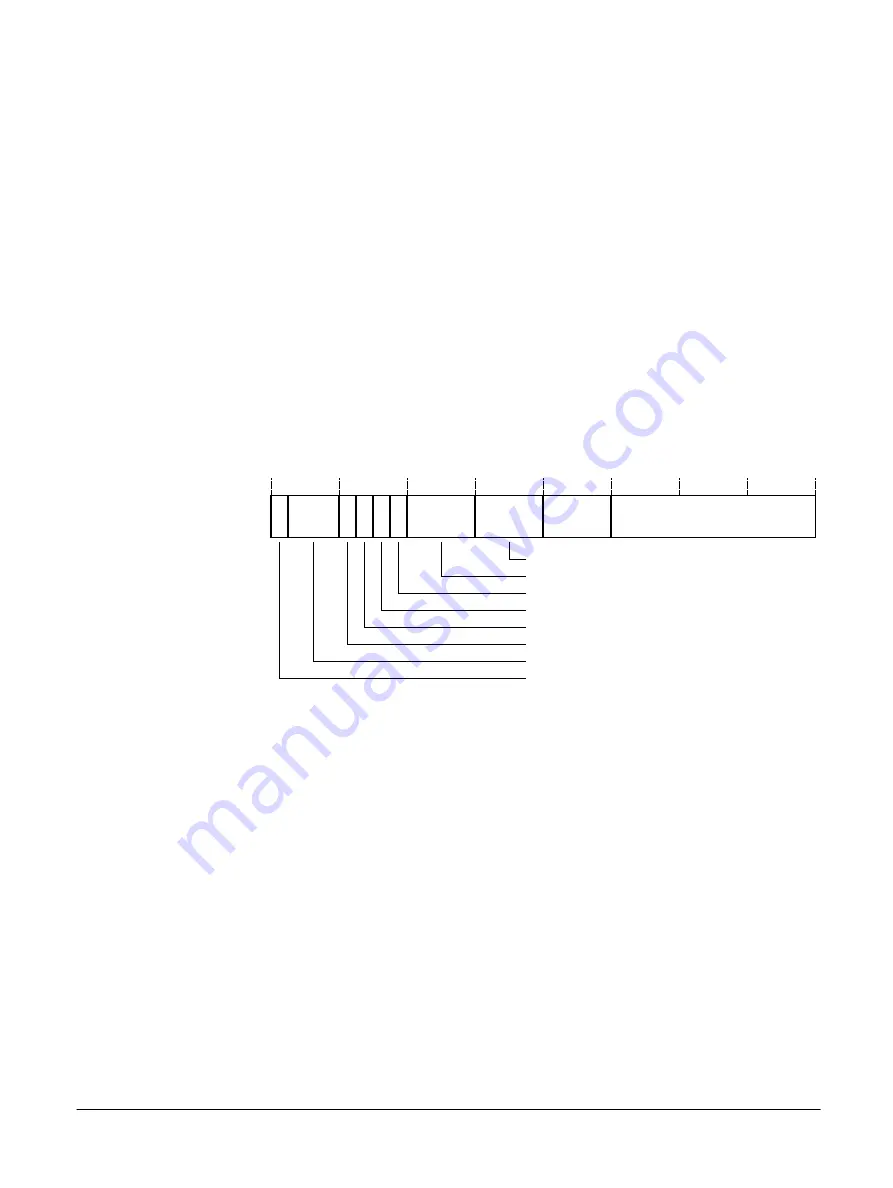

31

0

25 24

16 15

11

12

5 4

CCITMIN

30

28

20 19

RES

0

23

27 26

EXLEVEL_S

EXLEVEL_NS

NOOVERFLOW

NUMPROC

SYSSTALL

STALLCTL

SYNCPR

TRCERR

Figure C11-34 TRCIDR3 bit assignments

NOOVERFLOW, [31]

Indicates whether TRCSTALLCTLR.NOOVERFLOW is implemented:

0

TRCSTALLCTLR.NOOVERFLOW is not implemented.

NUMPROC, [30:28]

Indicates the number of cores available for tracing:

0b000

The trace unit can trace one processor, ETM trace unit sharing not supported.

SYSSTALL, [27]

Indicates whether stall control is implemented:

1

The system supports processor stall control.

STALLCTL, [26]

Indicates whether TRCSTALLCTLR is implemented:

1

TRCSTALLCTLR is implemented.

This field is used in conjunction with SYSSTALL.

C11 ETM registers

C11.35 ID Register 3

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

C11-778

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......