A8.2

Cache protection behavior

The configuration of the RAS extension that is implemented in the Cortex-A76 core includes cache

protection.

In this case, the Cortex-A76 core protects against errors that result in a RAM bitcell holding the incorrect

value.

The RAMs in the Cortex-A76 core have the following capability:

SED

Single Error Detect

. One bit of parity is applicable to the entire word. The word size is specific

for each RAM and depends on the protection granule.

Interleaved parity

One bit of parity is applicable to the even bits of the word, and one bit of parity is applicable to

the odd bits of the word.

SECDED

Single Error Correct, Double Error Detect

.

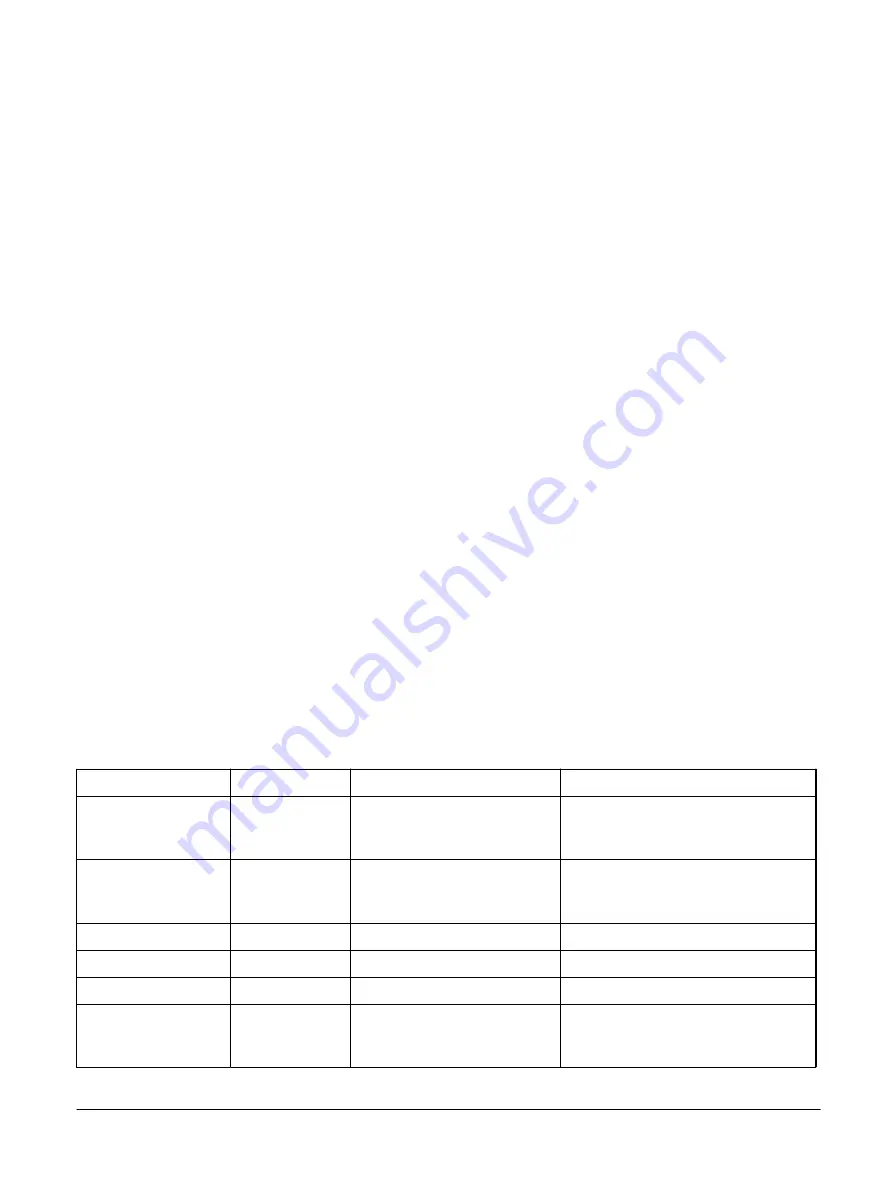

Table A8-1 Cache protection behavior

indicates which protection type is applied to

each RAM.

The core can progress and remain functionally correct when there is a single bit error in any RAM.

If there are multiple single bit errors in different RAMs, or within different protection granules within the

same RAM, then the core also remains functionally correct.

If there is a double bit error in a single RAM within the same protection granule, then the behavior

depends on the RAM:

• For RAMs with SECDED capability, the core detects and either reports or defers the error. If the error

is in a cache line containing dirty data, then that data might be lost.

• For RAMs with only SED, the core does not detect a double bit error. This might cause data

corruption.

If there are three or more bit errors within the same protection granule, then depending on the RAM and

the position of the errors within the RAM, the core might or might not detect the errors.

The cache protection feature of the core has a minimal performance impact when no errors are present.

Table A8-1 Cache protection behavior

RAM

Protection type

Protection granule

Correction behavior

L1 instruction cache tag

1 parity bit

31 bits

The line that contains the error is invalidated

from the L1 instruction cache and fetched

again from the subsequent memory system.

L1 instruction cache data

SED

72 bits

The line that contains the error is invalidated

from the L1 instruction cache and fetched

again from the subsequent memory system.

L1 BTB

None

-

-

L1 GHB

None

-

-

L1 BPIQ

None

-

-

L1 data cache tag

SECDED

34 bits + 7 bits for ECC attached to

the word.

The cache line that contains the error gets

evicted, corrected in line, and refilled to the

core.

A8 Reliability, Availability, and Serviceability (RAS)

A8.2 Cache protection behavior

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

A8-103

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......