B2.35

DISR_EL1, Deferred Interrupt Status Register, EL1

The DISR_EL1 records the SError interrupts consumed by an

ESB

instruction.

Bit field descriptions

DISR_EL1 is a 64-bit register, and is part of the registers

Reliability, Availability, Serviceability

(RAS)

functional group.

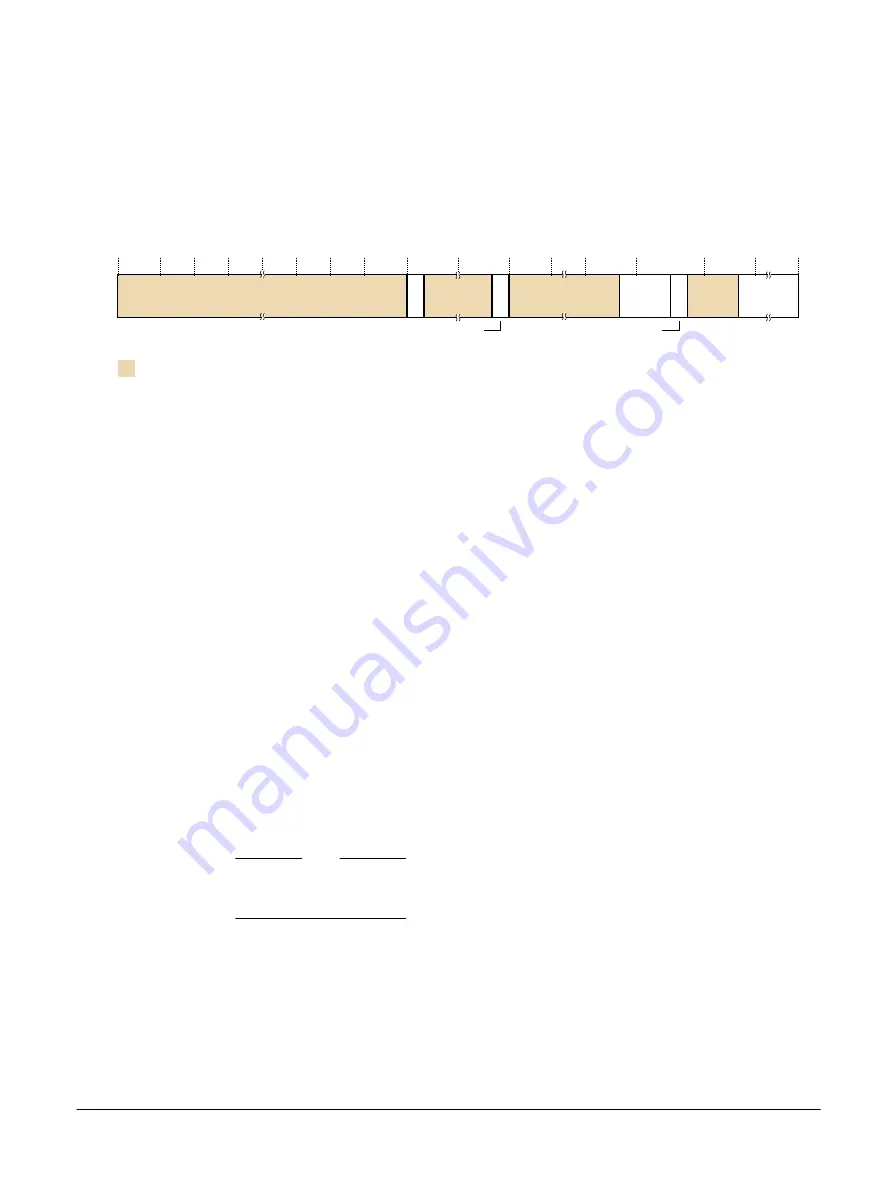

AET

DFSC

63

32

30

25 24

0

A

EA

RES

0

5

6

8

9

10

12

13

23

IDS

31

Figure B2-31 DISR_EL1 bit assignments, DISR_EL1.IDS is 0

RES0, [63:32]

Reserved,

RES0

.

A, [31]

Set to 1 when ESB defers an asynchronous SError interrupt. If the implementation does not

include any synchronizable sources of SError interrupt, this bit is

RES0

.

RES0, [30:25]

Reserved,

RES0

.

IDS, [24]

Indicates the type of format the deferred SError interrupt uses. The value of this bit is:

0

Deferred error uses architecturally-defined format.

RES0, [23:13]

Reserved,

RES0

.

AET, [12:10]

Asynchronous Error Type. Describes the state of the core after taking an asynchronous Data

Abort exception. The possible values are:

000

Uncontainable error (UC).

001

Unrecoverable error (UEU).

Note

The recovery software must also examine any implemented fault records to determine the

location and extent of the error.

EA, [9]

Reserved,

RES0

.

RES0, [8:6]

Reserved,

RES0

.

DFSC, [5:0]

Data Fault Status Code. The possible values of this field are:

B2 AArch64 system registers

B2.35 DISR_EL1, Deferred Interrupt Status Register, EL1

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

B2-194

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......