B2.78

ID_PFR1_EL1, AArch32 Processor Feature Register 1, EL1

The ID_PFR1_EL1 provides information about the programmers model and architecture extensions

supported by the core.

Bit field descriptions

ID_PFR1_EL1 is a 32-bit register, and is part of the Identification registers functional group.

This register is Read Only.

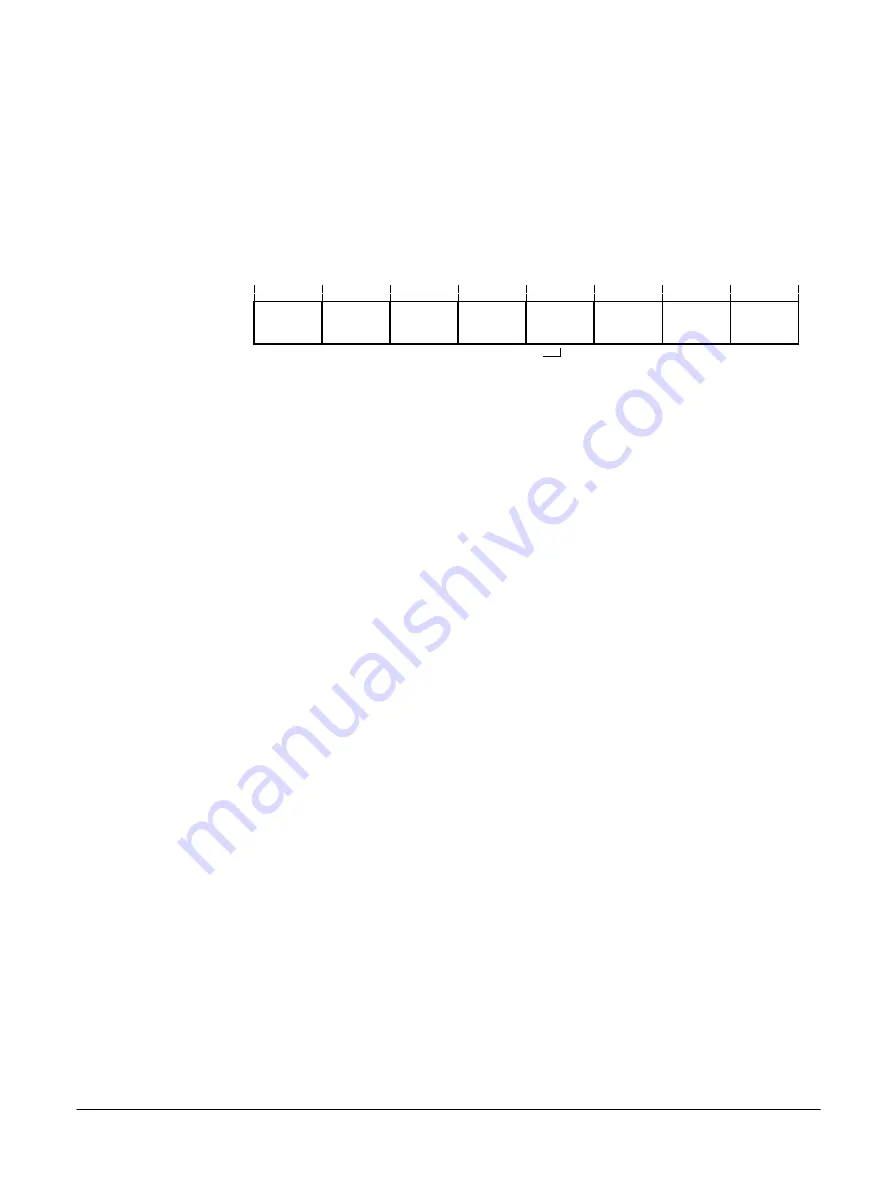

31

12 11

8 7

0

GIC CPU

4 3

16 15

Virtualization

20 19

27

28

GenTimer

MProgMod

Security

ProgMod

24 23

Virt_frac

Sec_frac

Figure B2-62 ID_PFR1_EL1 bit assignments

GIC CPU, [31:28]

GIC CPU support:

0

GIC CPU interface is disabled,

GICCDISABLE

is HIGH, or not implemented.

1

GIC CPU interface is implemented and enabled,

GICCDISABLE

is LOW.

Virt_frac, [27:24]

0

No features from the Armv7 Virtualization Extensions are implemented.

Sec_frac, [23:20]

0

No features from the Armv7 Virtualization Extensions are implemented.

GenTimer, [19:16]

Generic Timer support:

1

Generic Timer supported.

Virtualization, [15:12]

Virtualization support:

0

Virtualization not implemented.

MProgMod, [11:8]

M profile programmers model support:

0

Not supported.

Security, [7:4]

Security support:

0

Security not implemented.

ProgMod, [3:0]

Indicates support for the standard programmers model for Armv4 and later.

Model must support User, FIQ, IRQ, Supervisor, Abort, Undefined, and System modes:

0

Not supported.

B2 AArch64 system registers

B2.78 ID_PFR1_EL1, AArch32 Processor Feature Register 1, EL1

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

B2-258

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......