B2.86

PAR_EL1, Physical Address Register, EL1

The PAR_EL1 returns the output address from an address translation instruction that executed

successfully, or fault information if the instruction did not execute successfully.

Bit field descriptions, PAR_EL1.F is 0

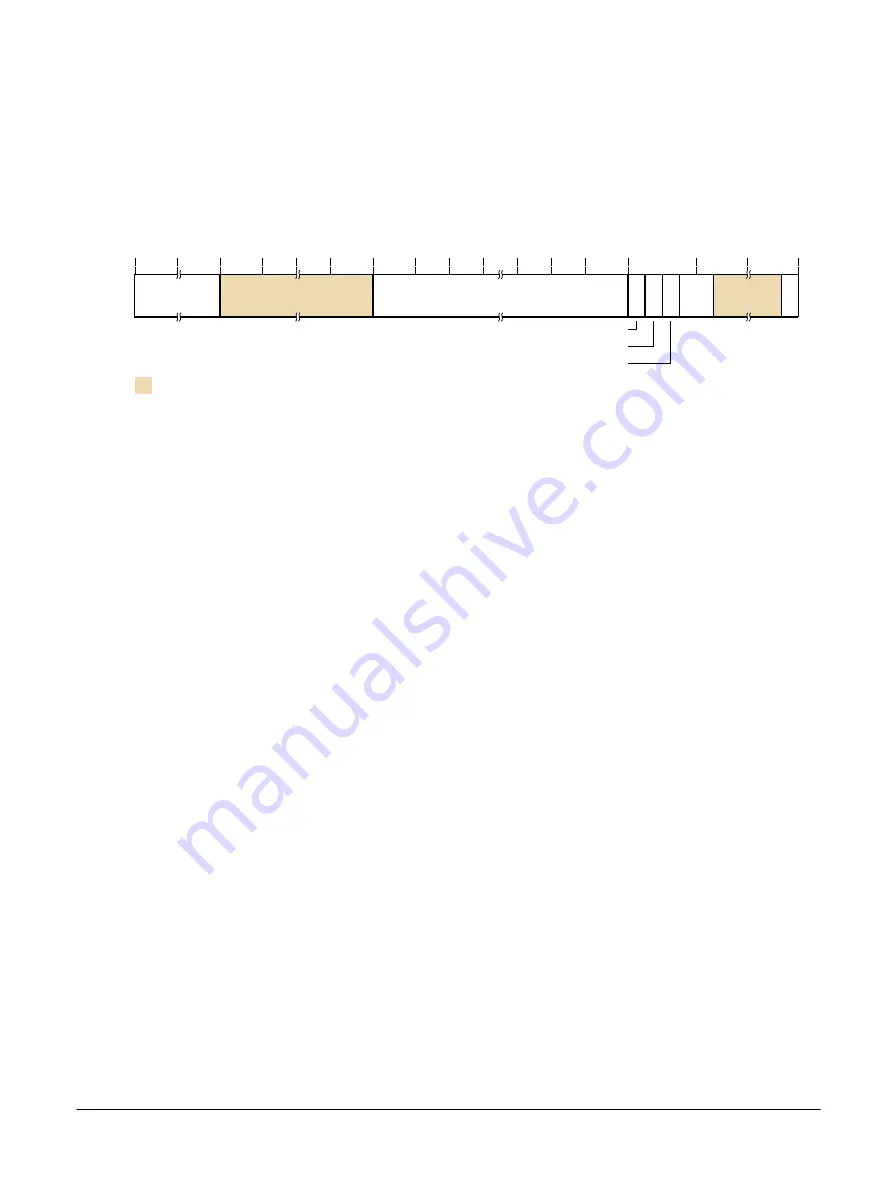

The following figure shows the PAR bit assignments when PAR.F is 0.

63

0

6

7

1

12

PA

LPAE

NS

8

9

10

11

IMP DEF

F

SH

39

40

55

56

ATTR

RES

0

Figure B2-70 PAR bit assignments, PAR_EL1.F is 0

IMP DEF, [10]

IMPLEMENTATION DEFINED

. Bit[10] is

RES0

.

F, [0]

Indicates whether the instruction performed a successful address translation.

0

Address translation completed successfully.

1

Address translation aborted.

Configurations

There are no configuration notes.

Bit fields and details that are not provided in this description are architecturally defined. See the

Arm

®

Architecture Reference Manual Armv8, for Armv8-A architecture profile

.

Bit field descriptions, PAR_EL1.F is 1

See the

Arm

®

Architecture Reference Manual Armv8, for Armv8-A architecture profile

.

B2 AArch64 system registers

B2.86 PAR_EL1, Physical Address Register, EL1

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

B2-269

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......