A1.4

Supported standards and specifications

The Cortex-A76 core implements the Armv8-A architecture and some architecture extensions. It also

supports interconnect, interrupt, timer, debug, and trace architectures.

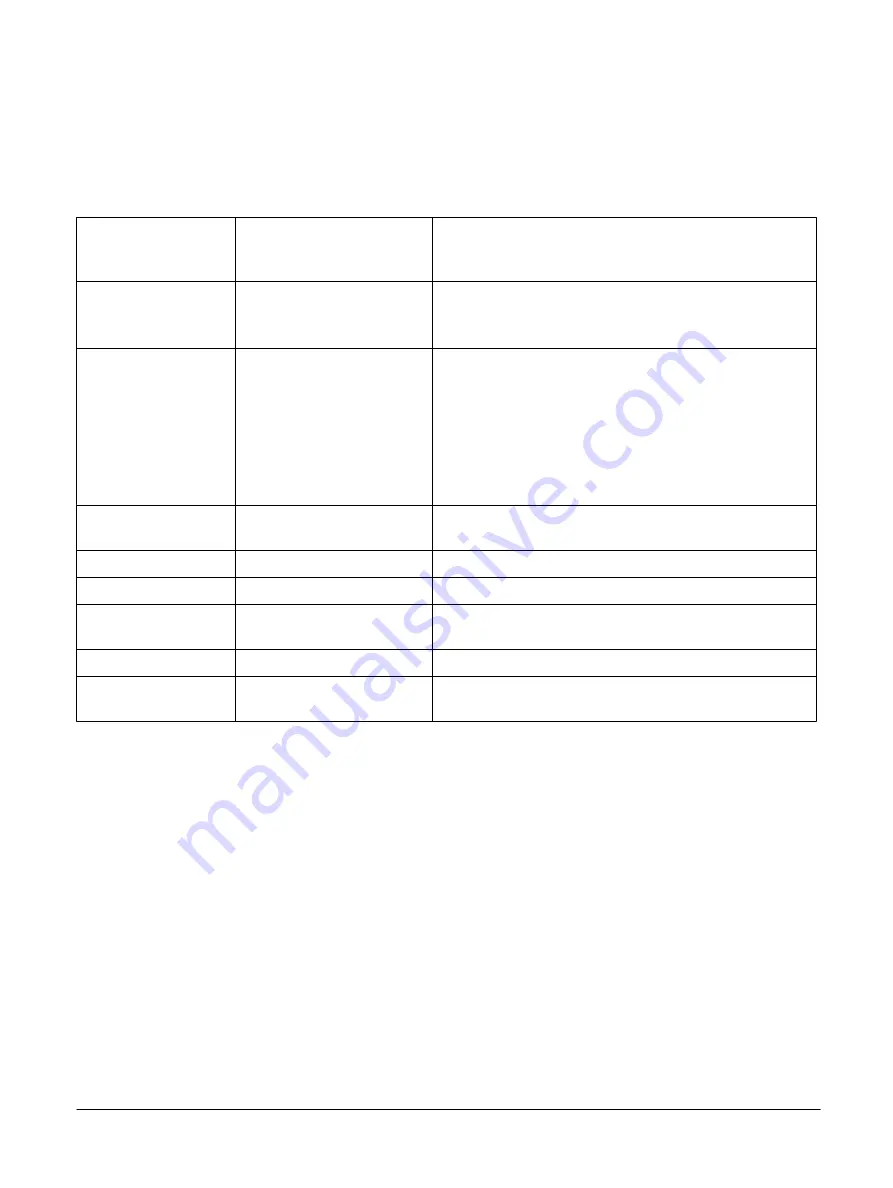

Table A1-2 Compliance with standards and specifications

Architecture

specification or

standard

Version

Notes

Arm architecture

Armv8-A

•

AArch32 execution state at Exception level EL0 only. AArch64

execution state at all Exception levels (EL0-EL3).

•

A64, A32, and T32 instruction sets.

Arm architecture

extensions

•

Armv8.1-A extensions

•

Armv8.2-A extensions

•

Cryptographic extension

•

RAS extension

•

Armv8.3-A extensions

•

Armv8.4-A dot product

instructions

•

Armv8.5-A extensions

•

The Cortex-A76 core implements the

LDAPR

instructions

introduced in the Armv8.3-A extensions.

•

The Cortex-A76 core optionally implements the

SDOT

and

UDOT

instructions introduced in the Armv8.4-A extensions.

•

The Cortex-A76 core implements the PSTATE

Speculative Store

Bypass Safe

(SSBS) bit introduced in the Armv8.5-A extension.

Generic Interrupt

Controller

GICv4

-

Generic Timer

Armv8-A

64-bit external system counter with timers within each core.

PMU

PMUv3

-

Debug

Armv8-A

With support for the debug features added by the Armv8.2-A

extensions.

CoreSight

CoreSightv3

-

Embedded Trace

Macrocell

ETMv4.2

Instruction trace only.

for a list of architectural references.

A1 Introduction

A1.4 Supported standards and specifications

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

A1-29

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......