Functional Description

ARM DDI 0275D

Copyright © 2002, 2003 ARM Limited. All rights reserved.

2-11

2.7

BIST interface

ATPG testing can only test out the interface between the ETB11 RAM and the ETB11.

It is unable to find faults in the actual RAM. A

Built-In Self Test

(BIST) interface is

required that fully tests the RAM.

ATPG vectors are created using Synopsys TetraMax. These enable the shadow logic

around the ETB11 RAM to be tested provided that the TetraMax has access to a model

of the RAM used. Greater than 99% stuck-at fault coverage can be achieved.

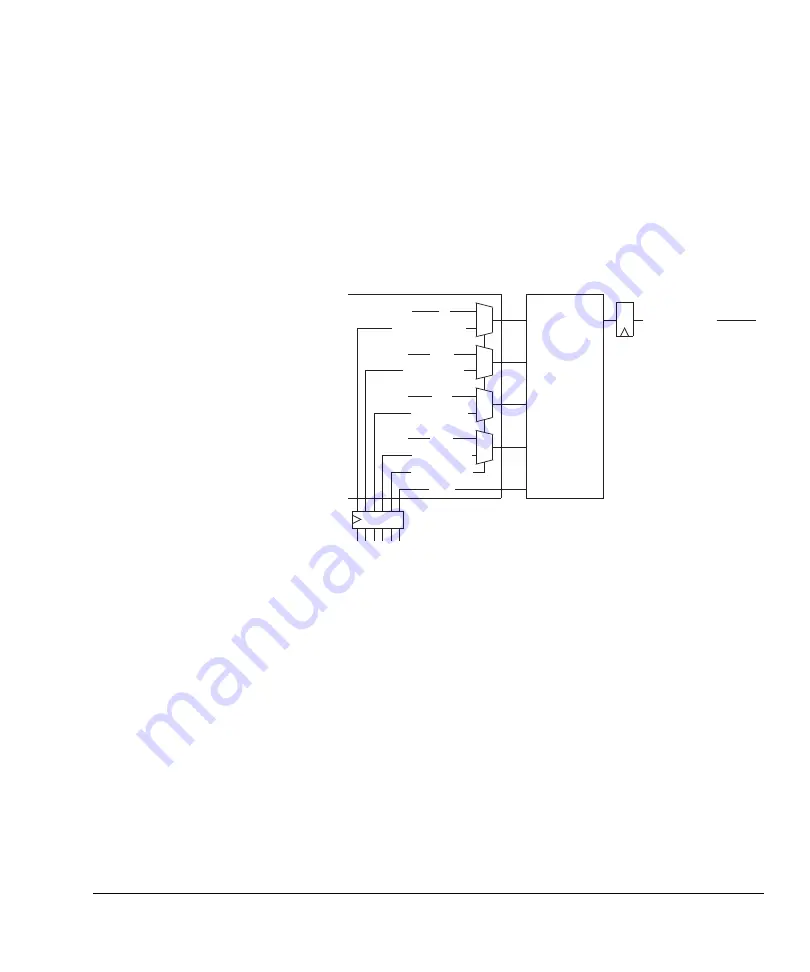

A block diagram of the BIST interface is shown in Figure 2-4.

Figure 2-4 BIST interface block diagram

The

MTESTON

signal gives an external BIST controller access to the inputs and

outputs of the ETB11 RAM. It is not possible for the ETB11 to operate in functional

mode when the BIST is testing the RAM. When

MTESTON

is HIGH do not:

•

set the TraceCaptEn bit

•

write to the ETB11 RAM

•

read from the ETB11 RAM.

A

MBISTADDR

DIN

MBISTDIN

CS

MBISTCE

WE

MBISTWE

MTESTON

CLK

Etb11Int

MBISTDOUT

ETB11 RAM

A

DIN

CS

WE

CLK

DOUT

Summary of Contents for ETB11

Page 6: ...List of Tables vi Copyright 2002 2003 ARM Limited All rights reserved ARM DDI 0275D ...

Page 8: ...List of Figures viii Copyright 2002 2003 ARM Limited All rights reserved ARM DDI 0275D ...

Page 46: ...Functional Description 2 26 Copyright 2002 2003 ARM Limited All rights reserved ARM DDI 0275D ...

Page 70: ...Signal Descriptions A 6 Copyright 2002 2003 ARM Limited All rights reserved ARM DDI 0275D ...

Page 78: ...Glossary Glossary 4 Copyright 2002 2003 ARM Limited All rights reserved ARM DDI 0275D ...