Interface Signal Function Selection Restrictions and Considerations

CYW920706WCDEVAL Hardware User Guide Doc. No.: 002-16535 Rev. **

31

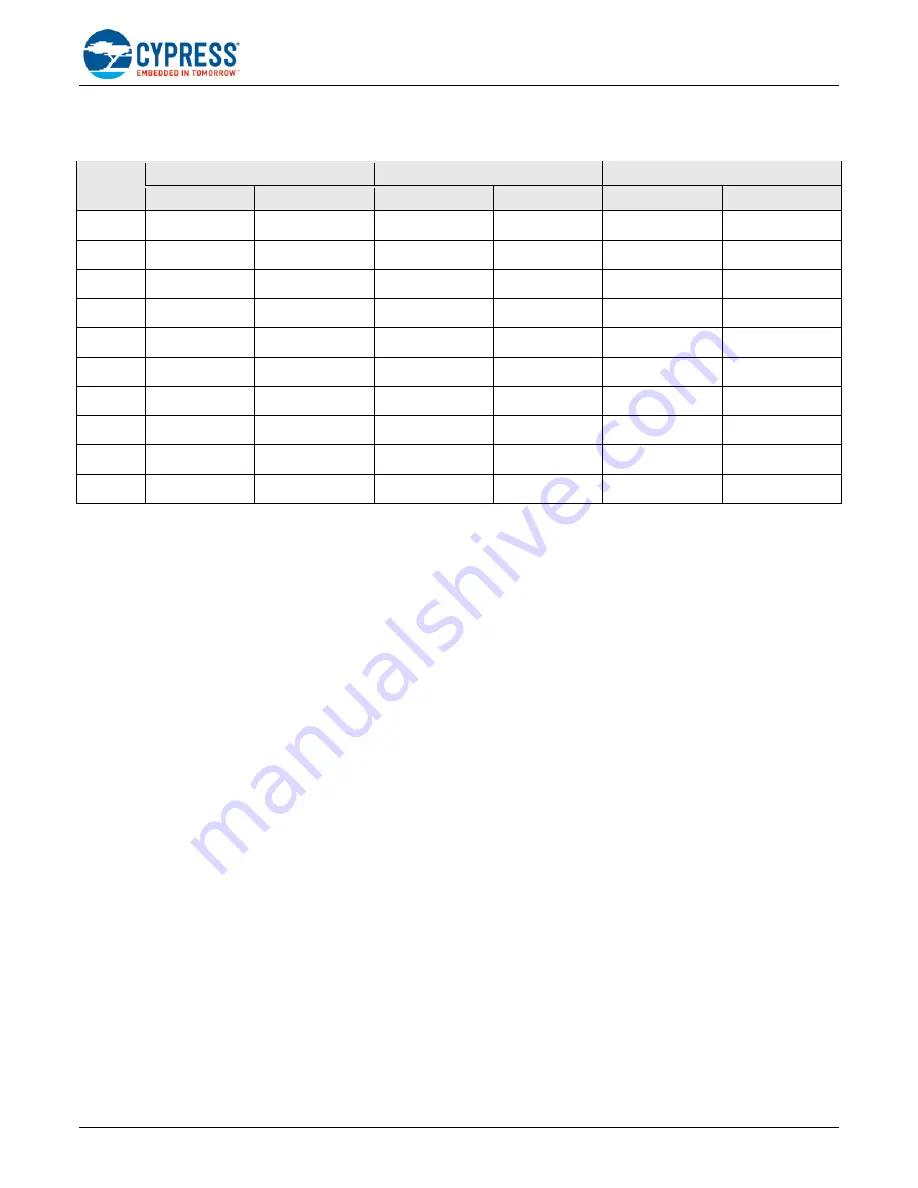

9.2.1.2 SPI1 Slave

shows CYW20706 SPI1 slave bus-configuration options.

Option

SPI1_CLK

SPI1_MOSI

SPI1_MISO

Pin

LHL GPIO Pxx

Pin

LHL GPIO Pxx

Pin

LHL GPIO Pxx

1

G8

P24

C5

P27

F7

P25

2

G8

P24

C5

P27

B7

P37

3

G8

P24

C5

P33

F7

P25

4

G8

P24

C5

P33

B7

P37

5

G8

P24

F8

P38

F7

P25

6

G8

P24

F8

P38

B7

P37

7

F8

P36

C5

P27

F7

P25

8

F8

P36

C5

P27

B7

P37

9

F8

P36

C5

P33

F7

P25

10

F8

P36

C5

P33

B7

P37

Table 9-3. CYW20706 SPI1 Slave Bus-Configuration Options

Note:

The bus signals of a peripheral UART (PUART) has certain restrictions if included in a system design that also uses the

” to understand how this restriction affects the bus configuration options of

both interfaces.

For a SPI1 slave programming example, see Section

9.2.2 SPI2

The SPI2 interface is provided as a CYW20706 connection to nonvolatile memory for accessing configuration, patches,

application code, and application data.

The SPI2 interface supports:

SPI clock modes 0 through 4.

A maximum transaction size of 254 bytes.

A maximum clock speed of 12 MHz for all I/O supply levels.

Operation as a master only.

The fixed-signal interface shown in

The firmware controls CS line assertion and de-assertion and can use the CS line to optimize transactions greater than 254

bytes.

For information on the API functions that support SPI2 access to attached serial flash or EEPROM, see WICED Studio header

files

wiced_hal_sflash.h

or

wiced_hal_seeprom.h

, respectively.

9.3 HCI UART

CYW20706 supports an HCI UART (also referred to as BT_UART). The following information applies to the HCI UART:

It is primarily used for programming and factory testing, but can also be used to support SWD debugging (see below).

It is a fixed (non-multiplexed) interface (see

).