Summary of Contents for PDF-10

Page 16: ......

Page 23: ...2 1 HALF WORD DATA TRANSMISSION 2 7 HRRO Half Word Right to Right Ones 560...

Page 35: ...2 4 SETCA LOGIC Set to Complement of AC 450...

Page 36: ...2 20 CENTRAL PROCESSOR 2 4 AND And with AC 404...

Page 37: ...2 4 ANDCB LOGIC And Complements of Both 440...

Page 38: ...2 22 CENTRAL PROCESSOR 2 4 ORCM Inclusive Or Complement of Memory with AC 464...

Page 48: ...2 32 CENTRAL PROCESSOR 2 6 ASHC Arithmetic Shift Combined Left Right...

Page 59: ...2 7 ARITHMETIC TESTING 2 43 CAI...

Page 74: ...2 58 CENTRAL PROCESSOR 2 9 JSP Jump and Save PC 1 36 1 47 us 265...

Page 79: ...2 9 POPJ PROGRAM CONTROL Pop Up and Jump 2 96 3 18 263...

Page 84: ...2 68 CENTRAL PROCESSOR 12 12 DFDV FDVL...

Page 85: ...2 12 COM INPUT OUTPUT Conditions In 4 87 4 98 jus 7...

Page 86: ...2 70 CONSO CENTRAL PROCESSOR Conditions In and Skip if One 2 12 4 11 4 22 jus 7...

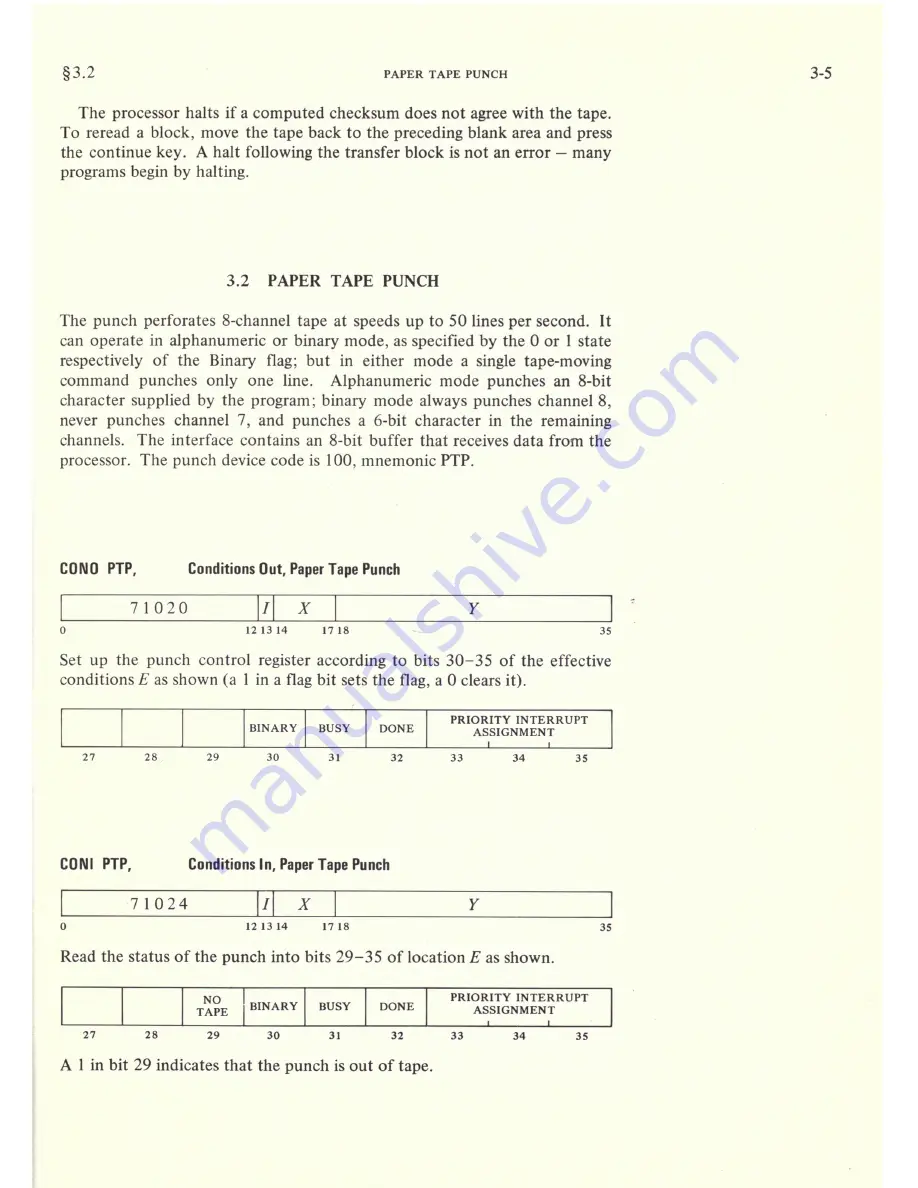

Page 98: ...3 2 BASIC IN OUT EQUIPMENT CONI PTR Conditions In Paper Tape Reader 3 1 71064...

Page 102: ...3 6 BASIC IN OUT EQUIPMENT DATAO FTP Data Out Paper Tape Punch 3 2 71014...

Page 105: ...3 3 TELETYPE 3 9 DATAI TTY Data In Teletype 71204...

Page 109: ...Appendices...

Page 110: ......

Page 112: ...A2 MNEMONICS E...

Page 114: ...A4 MNEMONICS 25510...

Page 115: ...NUMERIC LISTING A5 465...

Page 117: ...ALPHABETIC LISTING A7 FSC...

Page 120: ...A10 MNEMONICS...

Page 123: ...TELETYPE CODE B3 Even Parity Bit...

Page 124: ...B4 INPUT OUTPUT CODES Even Parity Bit 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1...

Page 125: ...TELETYPE CODE B5 Even...

Page 126: ...B6 INPUT OUTPUT CODES CARD CODES PDF 10...

Page 127: ...CARD CODES B7 Column...

Page 131: ...WORD FORMATS C3 BASIC INSTRUCTIONS INSTRUCTION CODE INCLUDING MODE...

Page 132: ...C4 MISCELLANY 10 L IF IN USER MODE INSTRUCTION TIMING FLOW CHART...

Page 133: ...INSTRUCTION TIMING C5 INSTRUCTION EXECUTION t...

Page 134: ...C6 MISCELLANY n S ri nm SiS5 fe tu 3s tat i S 5 J p Sp Jp dim Sa...

Page 135: ...IN OUT DEVICE BIT ASSIGNMENTS C7...

Page 136: ...C8 MISCELLANY N ed M o o 03 O o o s OH O s 4 c C3 c 03 CJ 3 c OH O...

Page 137: ...INDICATOR PANELS C9 a o o o 6 o o u n a T3 C 05 m VO O E v O o 03 o O...