4. History Data Details

4. History Data Details

This section describes the IDE and USB related history data displayed.

4.1

IDE History Data

Table 4-1 shows the IDE-related history data. The signal descriptions are based on the ATA/ATAPI

standard signal naming conventions. Refer to Table A-1 for correspondence to the LSI pin names.

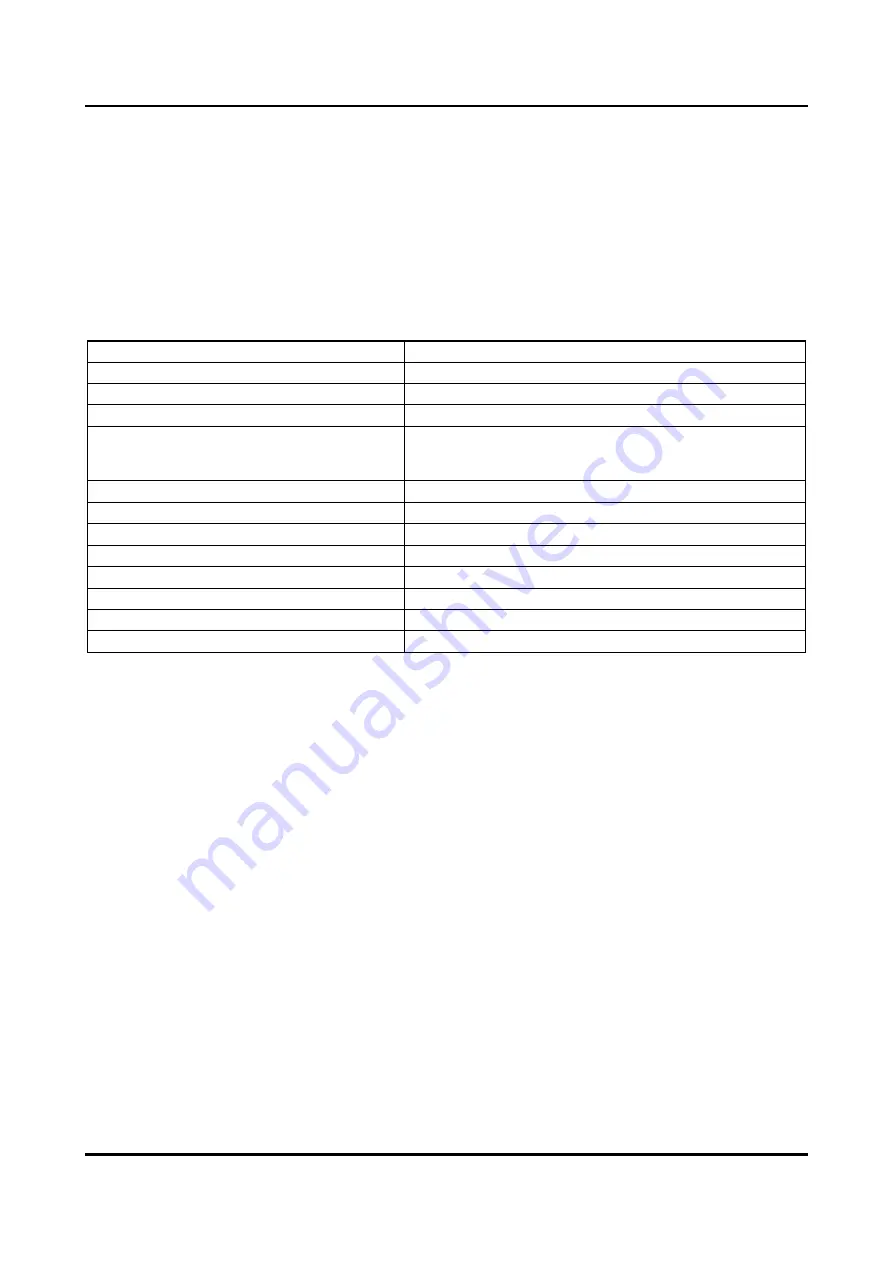

Table 4-1 IDE history data list

History data

Summary

IDE: idle

Idle state

IDE: Hardware reset

Detected hardware reset.

IDE: SRST

Detected software reset.

IDE: command [xxh]

Detected ATA/ATAPI command receipt. “xx” indicates

hexadecimal command code (operation code for ATAPI)

received.

IDE: PIO (D->H)

Transferred PIO data from device to host.

IDE: PIO (H->D)

Transferred PIO data from host to device.

IDE: Multi Word DMA (D->H)

Transferred Multi Word DMA data from device to host.

IDE: Multi Word DMA (H->D)

Transferred Multi Word DMA data from host to device.

IDE: Ultra DMA (D->H)

Transferred Ultra DMA data from device to host.

IDE: Ultra DMA (H->D)

Transferred Ultra DMA data from host to device.

IDE: CRC error

Detected CRC error during Ultra DMA data transfer.

IDE: INTRQ

Asserted INTRQ.

4.1.1 IDE:

idle

This history entry is recorded when in a state that allows commands to be received from

the main CPU (when the Status register BSY bit and DRQ bit are both 0), corresponding to

the state in which LSI power has been turned on or reset or a command has finished

executing. If the main CPU reads the Status register BSY bit as 1 although the history data

has not changed from this state, there may be a problem with signal quality or in the signal

connections shown below.

•

CS0-, DA0 to DA2, DD0 to DD7,

DIOR-

4.1.2

IDE: Hardware reset

This history entry is recorded when a hardware reset is detected. If this history entry does

not appear even after the main CPU has issued a hardware reset, there may be a problem

with signal quality or in the signal connection shown below.

•

RESET-

6

EPSON

S1R72U16 Development Support

Manual (Rev.2.00)