4. MAC ADDRESS SETTING

S1S60000 Application Note No.2 (Rev.1.1)

EPSON

11

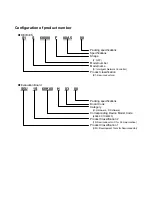

Written data row for each host CPU type are as follows.

Table 4.6 Data row for each host CPU type

Host CPU type

Data row

8-bit connection

LittleEndian

0x00,0x00,0x00,0x00,0x01,0x04,0x00,0x02,0x00,0x00,0x00,0x00,0xff,0xff,0x14,0x48

8-bit connection

BigEndian

0x00,0x00,0x00,0x00,0x01,0x04,0x00,0x02,0x00,0x00,0x00,0x00,0xff,0xff,0x14,0x48

16-bit connection

LittleEndian

0x0000,0x0000,0x0401,0x0200,0x0000,0x0000,0xffff,0x4814

16-bit connection

BigEndian

0x0000,0x0000,0x0104,0x0002,0x0000,0x0000,0xffff,0x1448

* Access sequence in the case of 8-bit connection: low-order port

→

high-order port

S1S60000 returns the “ok” status (0x0303). Setting at the “0x4814” part of 16-bit to 31-bit of the MAC address

is complete.

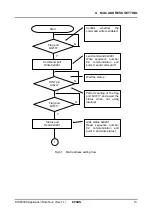

At last, write the remaining “0x0123” of the MAC address at the offset address 03h of the internal register. In

the same manner, write the “send” command (0x0401), read the “write” status (0x0401), and write the option

parameters. The sequence number has been set to 4 in increment by 1.

Write the following data row to the data port. The difference from the second setting is the offset addresses of

internal register at BYTE 6 and 7 and the MAC address at BYTE 14 and 15 (the hatched areas of the table).

Table 4.7 Send command option parameters

BYTE Write

data

Contents

Comment

0

0x00

1

0x00

Transmission data

In the case of internal register, there is no

data following the command options.

2

0x00

Flag

0 when the SYSTEM communication end

point is accessed.

3

0x00 Fixed

value

4

0x01 Operation

Write

(Write

to the internal register)

5

0x04

Object

Internal register of S1S60000

6

0x00

7

0x03

Offset

Internal register/offset address

0x0003

8

0x00

9

0x00

10

0x00

11

0x00

Fixed value

Fixed value 0 when the internal register is

accessed

12

0xff

13

0xff

Bit mask

Specify 1 as the operation object bit.

14

0x23

15

0x01

Bit pattern

Write value (the subsequent MAC address

0123)

When the option parameters are stored in the memory, BYTE0 in Table 4.7 is set to the low-order address of the

memory.

Write data row for each host CPU type are as follows.