5

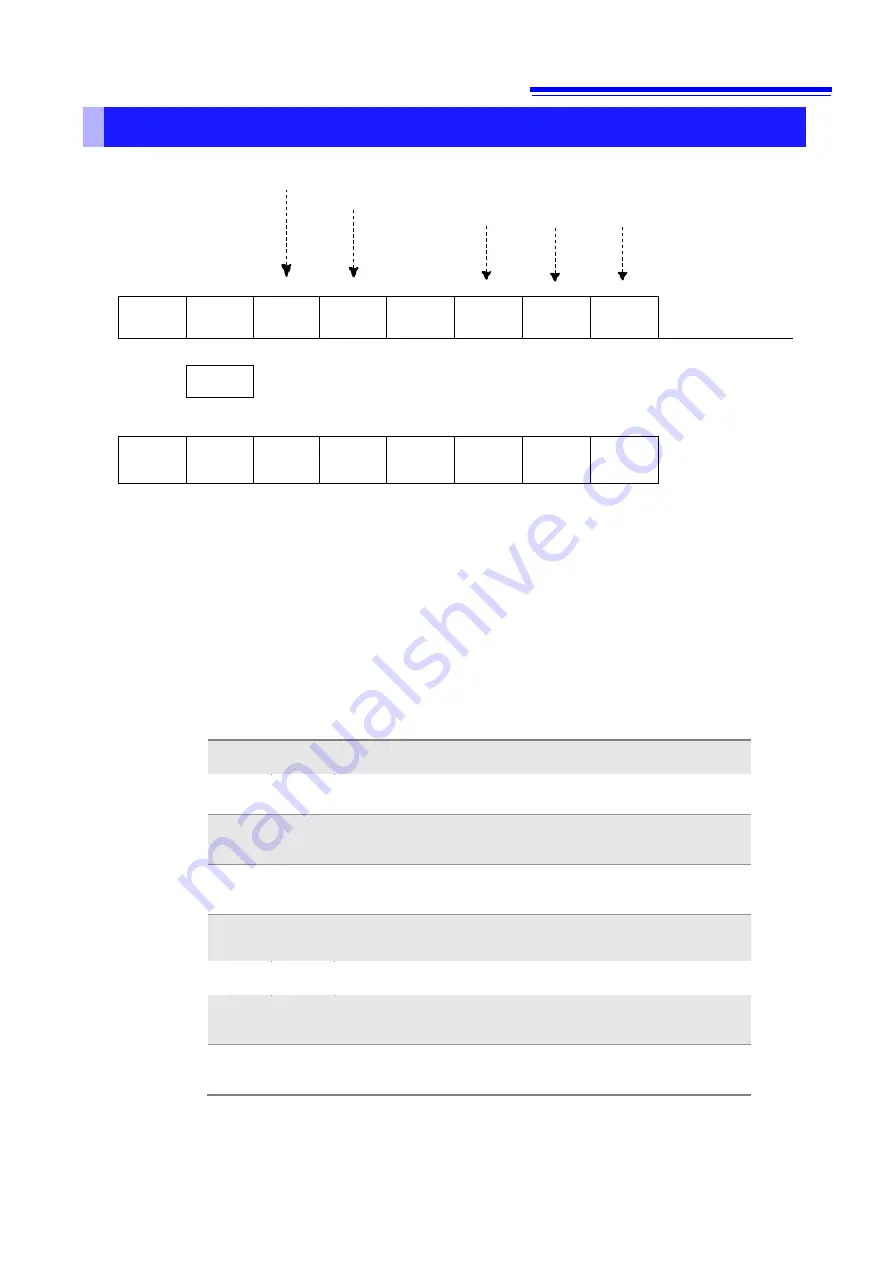

Status Byte Register

Standard Event Register Description

Output Queue data information

Each of these bits corresponds to a specific event register

bit7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

Unused

MSS

ESB

MAV

DSB

Unused Unused Unused

Status Byte

Register (STB)

↑

↓

↓

↓

↓

↓

↓

Logical

sum

←

&

&

&

&

&

&

↑

↑

↑

↑

↑

↑

bit7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

Unused

0

ESB

MAV

DSB

Unused Unused Unused

Service Request

Enable Register

(SRER)

Overview of Service Request Occurrence

The Status Byte Register contains information about the event registers and the output queue. Required items are

selected from this information by masking with the Service Request Enable Register. When any bit selected by the

mask is set, bit 6 (MSS; the Master Summary Status) of the Status Byte Register is also set.

Status Byte Register (STB)

When any Status Byte Register bit enabled by the Service Request Enable Register has switched from 0 to 1, the

MSS bit becomes 1.

Although the MSS bit is only read by an

*STB?

query, it is not cleared until a clear event is initiated by the

*CLS

command.

Bit 7

ERR

Bit 6

MSS This is the logical sum of the other bits of the Status Byte Register.

Bit 5

ESB

Standard Event Status (logical sum) bit

This is logical sum of the Standard Event Status Register.

Bit 4

MAV

Message arrival

Bit 3

DSB

Event summary (logical sum) bit 1

This is logical sum of the Event Status Register.

Bit 2

-

Unused

Bit 1

-

Unused

Bit 0

-

Unused

Service Request Enable Register (SRER)

This register masks the Status Byte Register. Setting a bit of this register to 1 enables the corresponding bit of the

Status Byte Register to be used.

Summary of Contents for Super megohm SM7110

Page 51: ......