3. Data Path > Transaction Management

23

PEB383 User Manual

July 25, 2011

Integrated Device Technology, Inc.

Confidential - NDA Required

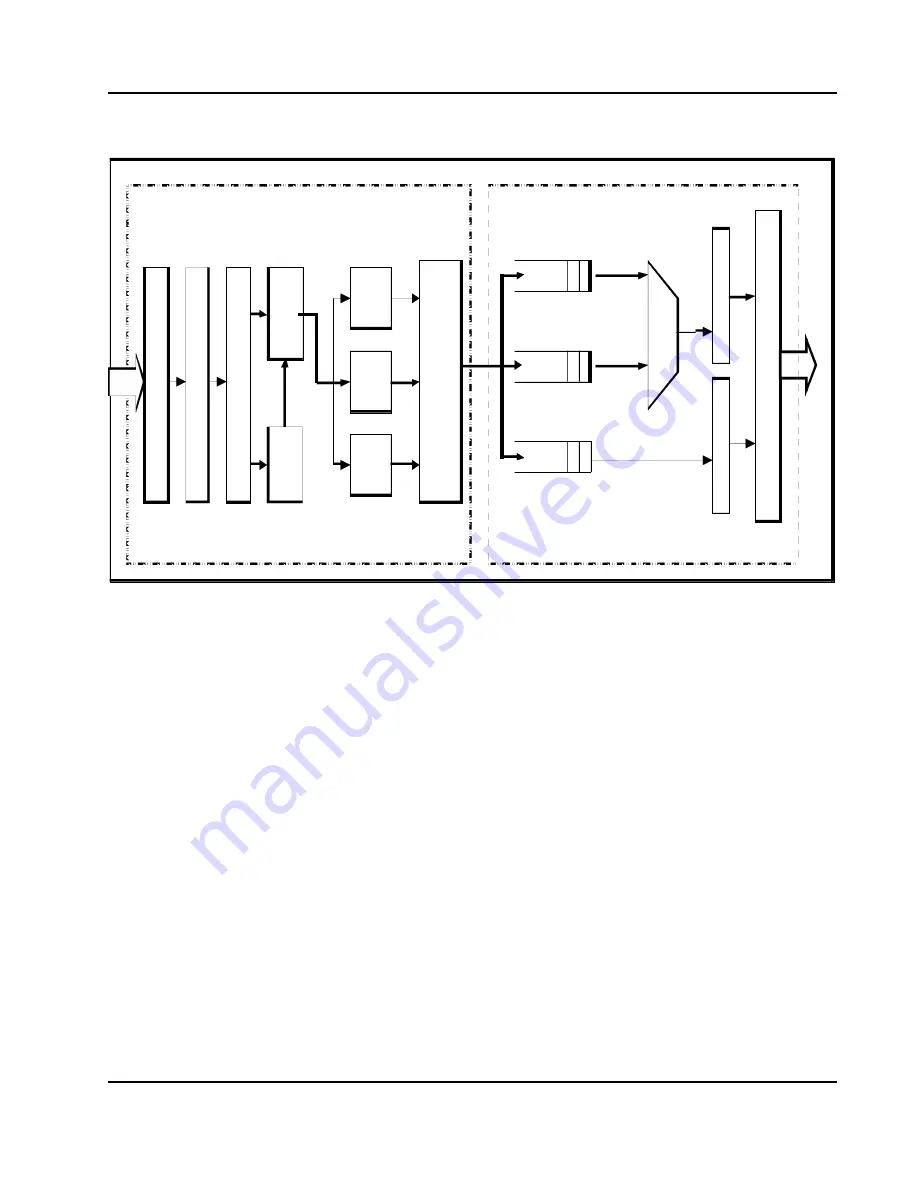

Figure 8: Downstream Data Path

3.2

Transaction Management

The following sub-sections describe how the PEB383 handles upstream and downstream transactions.

3.2.1

Upstream Transaction Management

Transactions that originate on the PCI Interface that are destined for the PCIe Interface are stored in the

respective queues or buffers in the PCI clock domain, and are then forwarded to the PCIe Core (see

). PCI buffer logic decomposes the received transactions as per the PCIe constraints (for

example, MAX_RD_SIZE, MAX_PAY_SIZE, RCB, and 4-KB address boundary). Three sets of data

and control signals for the three types of transactions (posted, non-posted, and completions) are used

between the PCI and PCIe Cores.

Transactions are stored temporarily in the PCIe Core buffers before they are used to construct TLPs,

and are then made visible to TLP arbiter. The TLPs are processed by the TLP arbiter only after

ordering rules are satisfied. The TLP arbiter selects one of the five input TLPs (error message, PME

message, posted, completion, and non-posted TLPs) in a round-robin mode if sufficient credits and

retry buffer space is available for the specific TLPs. The TLP arbiter continues to check the available

credit and retry buffer space against each of the active inputs, and selects the one that meets the

constraint. The ECRC adder calculates and appends a 32-bit ECRC value to the end of the TLP

selected by the arbiter if ECRC generation is enabled by software, and then forwards the TLP to the

Data link layer.

P

C

I

In

te

rfa

ce

R

x

S

E

R

D

E

S

D

e

-sc

ra

m

b

le

r

B

y

te

U

n

-s

tri

p

er

LCRC

Checker

Packet

Decoder

Address

Decoder

ECRC

Checker

TLP

Error

Detecter

Reques t

Generator

A

rb

ite

r

M

a

ste

r I

n

ter

fac

e

T

ar

g

e

t I

n

te

rfa

ce

Posted Buf fer

(512 Bytes )

Non-Posted Queue

4 Entries

Upstream Read

Completion Buffer

(1 KB)

PCIe Core

PCI Co re

Receiv e Flo w

Contr ol B uffer s

Delayed Completion

Devi ce Co re Interface