8. Error Handling

159

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

itemizes the error cases detected and reported by the PB master and the PB slave. Error

logging in PB_ERRCS and PB_AERR is triggered for each of the error cases outlined in

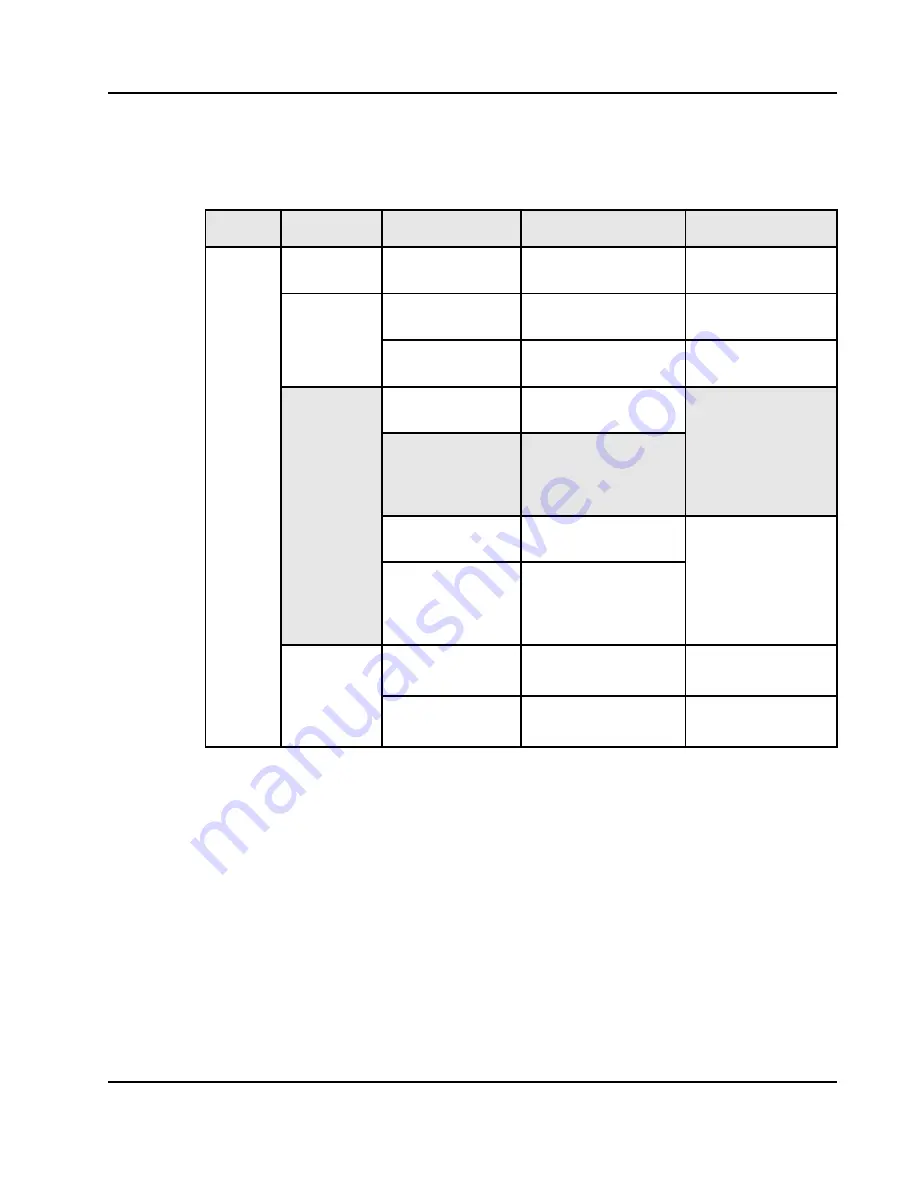

Table 40: PB Interface Errors

Interface

Error

Destination/Source

Conditions

Reporting

PB slave

Address parity

PCI-1, PCI-2,

Registers

Address only, Write, Read

PB_A_PAR in the ISR1

register

Data parity

PCI-1, Registers

Write

PB_P1_D_PAR in the

ISR1 register

PCI-2

Write

PB_P2_D_PAR in the

ISR1 register

Illegal access

PCI-1 (Memory)

Unaligned access in

PPC

little-endian

mode

PB_TEA if TEA_EN=1,

PB_P1_ERR in the

ISR1 register

PCI-1 (Configuration,

IO, IACK)

Registers

Unaligned access in

PPC

little-endian

mode,

Transaction Size > 4 bytes

or burst

PCI-2 (Memory)

Unaligned access in

PPC

little-endian

mode

PB_TEA if TEA_EN=1,

PB_P2_ERR in the

ISR1 register

PCI-2 (Configuration,

IO, IACK)

Unaligned access in

PPC

little-endian

mode,

Transaction Size > 4 bytes

or burst

Propagation of

error from

destination

master

PCI-1

Read

PB_TEA if

TEA_EN=1

PCI-2

Read

PB_TEA if

TEA_EN=1