ADwin-Pro II

Hardware, manual Dec. 2018

111

Pro II: Digital-I/O Modules

Pro II-DIO-32/1-TiCo Rev. E

ADwin

5.7.3 Pro II-DIO-32/1-TiCo Rev. E

The digital input/output module Pro II-DIO-32/1-TiCo Rev. E provides 32 pro-

grammable digital input and output channels at TTL levels. Each of the chan-

nels can be configured as input or output by

ADbasic

instructions. The chan-

nels are configured as inputs after power up.

Edge monitor

The module can automatically monitor the edges of input channels, which is

performed with a frequency of 100MHz. With every change, the current input

levels are saved together with a time stamp in a FIFO; up to 511 of those value

pairs (input level and time stamp) can be stored. The FIFO data can be read

and processed.

In addition, one can query whether a positive or negative edge has occurred

at the input channels.

Spike filter

At the input channels spikes can be suppressed using an adjustable filter. Each

channel has its own filter, but filter settings are the same for all channels. After

power-up, all filters are disabled.

TiCo processor

The module provides in addition the freely programmable

TiCo

processor with

28KiB program memory and 28KiB data memory. The

TiCo

processor has

access to all digital input and output channels. Find more information about

use and programming of the

TiCo

processor in the

TiCoBasic

manual.

If you store a

TiCoBasic

program in the

TiCo

bootloader, the program is auto-

matically loaded into the

TiCo

processor and started on power-up. Thus, the

module can run on its own and independently from the CPU module of the

ADwin-Pro II

system.

Timed level output

The module may output levels at defined points in time to digital outputs as

stand-alone. A FIFO serves as buffer where the user-defined level patterns

and points in time are stored.

The Fifo can either be used for edge control of the inputs or for level output at

the outputs.

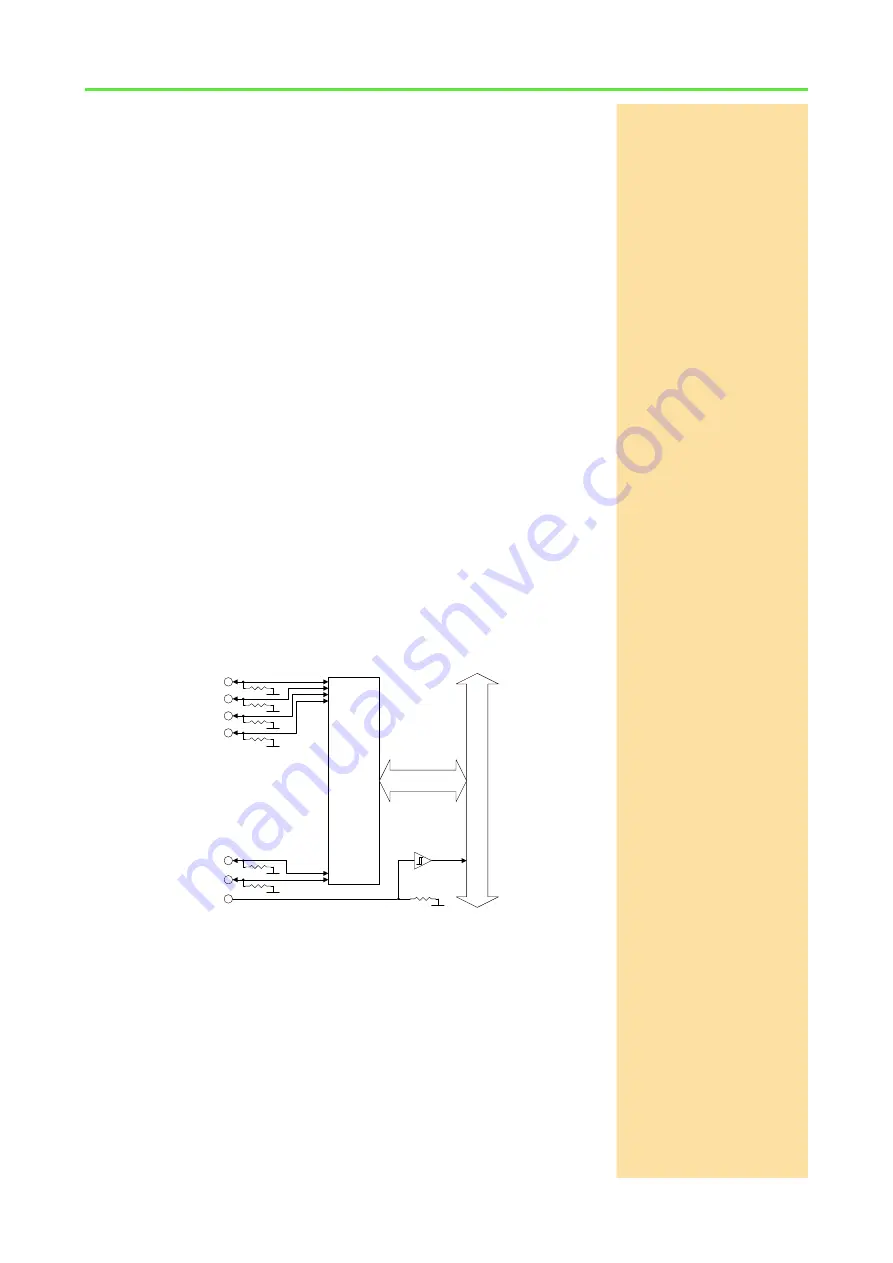

Fig. 95 – Pro II-DIO-32/1-TiCo Rev. E: Block diagram

ADwin-Pro

II

bus

0

1

31

...........

..........................

2

3

30

EVENT

Data

Register

Data

2k2

4k7

2k2

2k2

2k2

2k2

2k2