Soft Memory Controller Fabric Interface Controller

Microsemi Proprietary UG0446 User Guide Revision 7.0

224

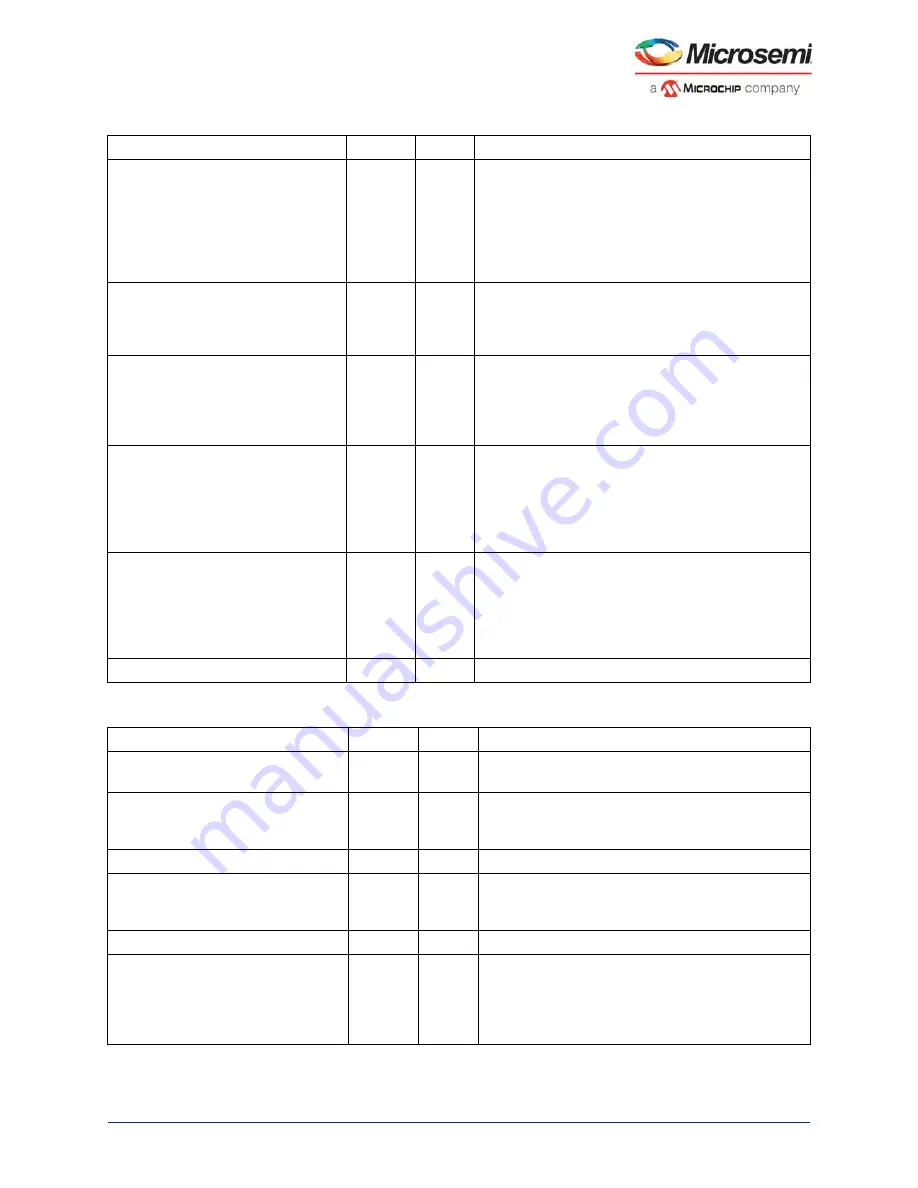

MDDR_SMC_AXI_M_ARLOCK[1:0]

Output

Indicates lock type. This signal provides additional

information about the atomic characteristics of the read

transfer.

00: Normal access

01: Exclusive access

10: Locked access

11: Reserved

MDDR_SMC_AXI_M_BID[3:0]

Input

Indicates response ID. The identification tag of the write

response. The MDDR_SMC_AXI_M_BID

value must

match the MDDR_SMC_AXI_M_AWID

value of the

write transaction to which the slave is responding.

MDDR_SMC_AXI_M_RID[3:0]

Input

Read ID tag. This signal is the ID tag of the read data

group of signals. The MDDR_SMC_AXI_M_RID

value

is generated by the slave and must match the

MDDR_SMC_AXI_M_ARID

value of the read

transaction to which it is responding.

MDDR_SMC_AXI_M_RRESP[1:0]

Input

Indicates read response. This signal indicates the

status of the read transfer.

00: Normal access okay

01: Exclusive access okay

10: Slave error

11: Decode error

MDDR_SMC_AXI_M_BRESP[1:0]

Input

Indicates write response. This signal indicates the

status of the write transaction.

00: Normal access okay

01: Exclusive access okay

10: Slave error

11: Decode error

MDDR_SMC_AXI_M_RDATA[63:0]

Input

Indicates read data.

Table 167 •

SMC_FIC 32-bit AHB-Lite Port List

Signal

Direction Polarity Description

MDDR_SMC_AHB_M_HMASTLOCK

Output

High

Indicates that the current master is performing a locked

sequence of transfers.

MDDR_SMC_AHB_M_HWRITE

Output

High

Indicates write control signal. When High, this signal

indicates a write transfer, and when Low, a read

transfer.

MDDR_SMC_AHB_M_HRESP

Input

High

The transfer response indicates the status of transfer.

MDDR_SMC_AHB_M_HREADY

Input

High

When High, the signal indicates that a transfer has

been completed on the bus. This signal may be driven

Low to extend a transfer.

MDDR_SMC_AHB_M_HBURST[1:0]

Output

Indicates the burst type.

MDDR_SMC_AHB_M_HTRANS[1:0]

Output

Indicates the type of the current transfer.

00: Idle

01: Busy

10: Non-sequential

11: Sequential

Table 166 •

SMC_FIC 64-bit AXI Port List

(continued)

Signal

Direction Polarity Description