Soft Memory Controller Fabric Interface Controller

Microsemi Proprietary UG0446 User Guide Revision 7.0

228

6.4.2

Use Model 1: Accessing SDRAM from MSS Through

CoreSDR_AXI

This use model describes how to use the SMC_FIC to access external SDR memory from MSS. It uses

the AXI interface of SMC_FIC to connect to CoreSDR_AXI. CoreSDR_AXI is an AXI-based SDR

memory controller. The steps provided below are required to access the external SDR memory from

CoreSDR_AXI.

1.

Instantiate the SmartFusion2 MSS component onto the SmartDesign canvas.

2.

Configure the SmartFusion2 MSS peripheral components to meet application needs using MSS

configurator.

3.

Configure the external memory interface type and select

Using an AXI Interface

, as shown in the

previous image.

4.

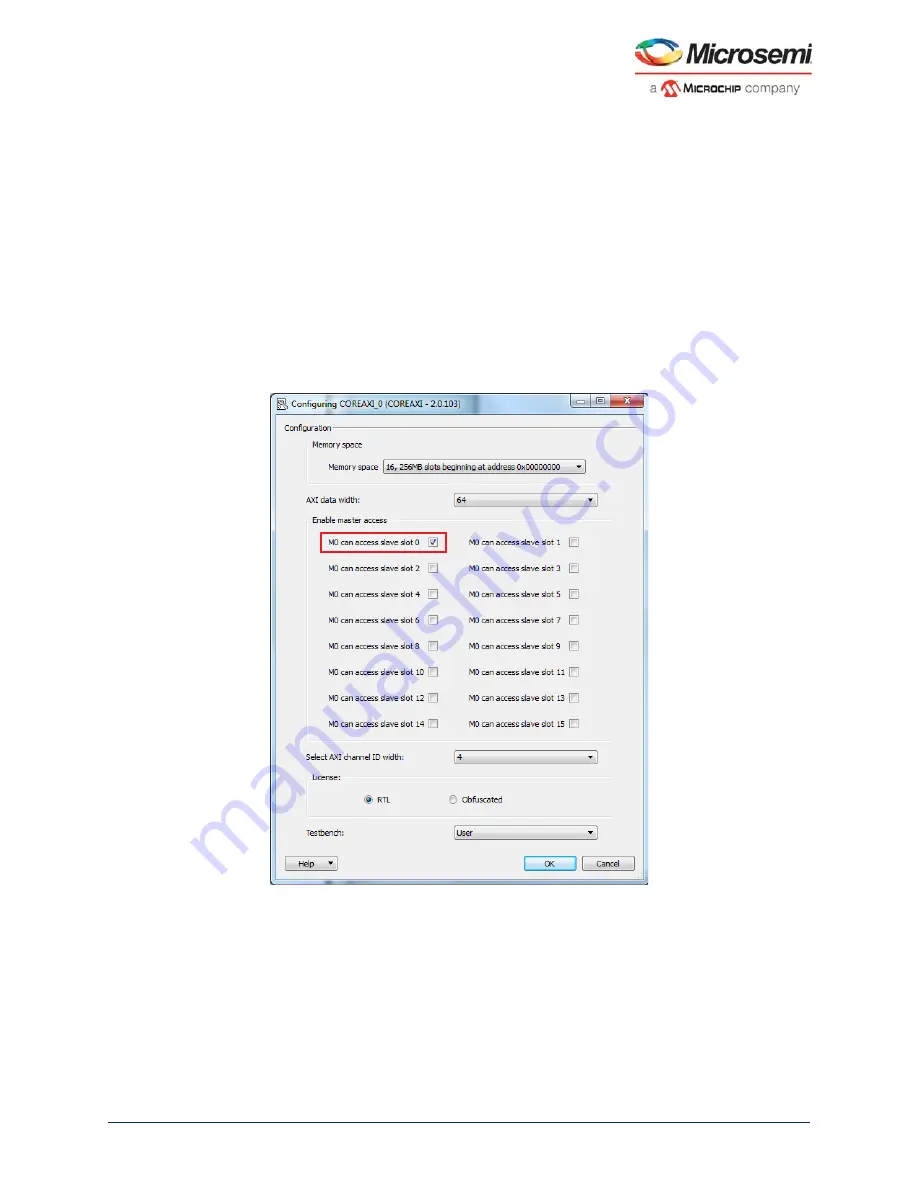

Instantiate and configure CoreAXI so that the master slot M0 is enabled for the slave slot S0, as

shown in the following image. The slot size selection must be matched with the amount of external

memory space.

Figure 144 •

Core_AXI Configuration

5.

Instantiate and configure CoreSDR_AXI to match the external memory parameters.

6.

Connect the subsystem together as shown in the following image. Connect the MSS SMC_FIC

master interface port, MDDR_SMC_AXI_MASTER, to the CoreAXI bus mirrored-master M0.

Connect the CoreAXI mirrored-slave bus interface (BIF) port S0 to the slave BIF port of the

CoreSDR_AXI core instance.