3-12

MPC8240 Integrated Processor User’s Manual

Address Translation

.

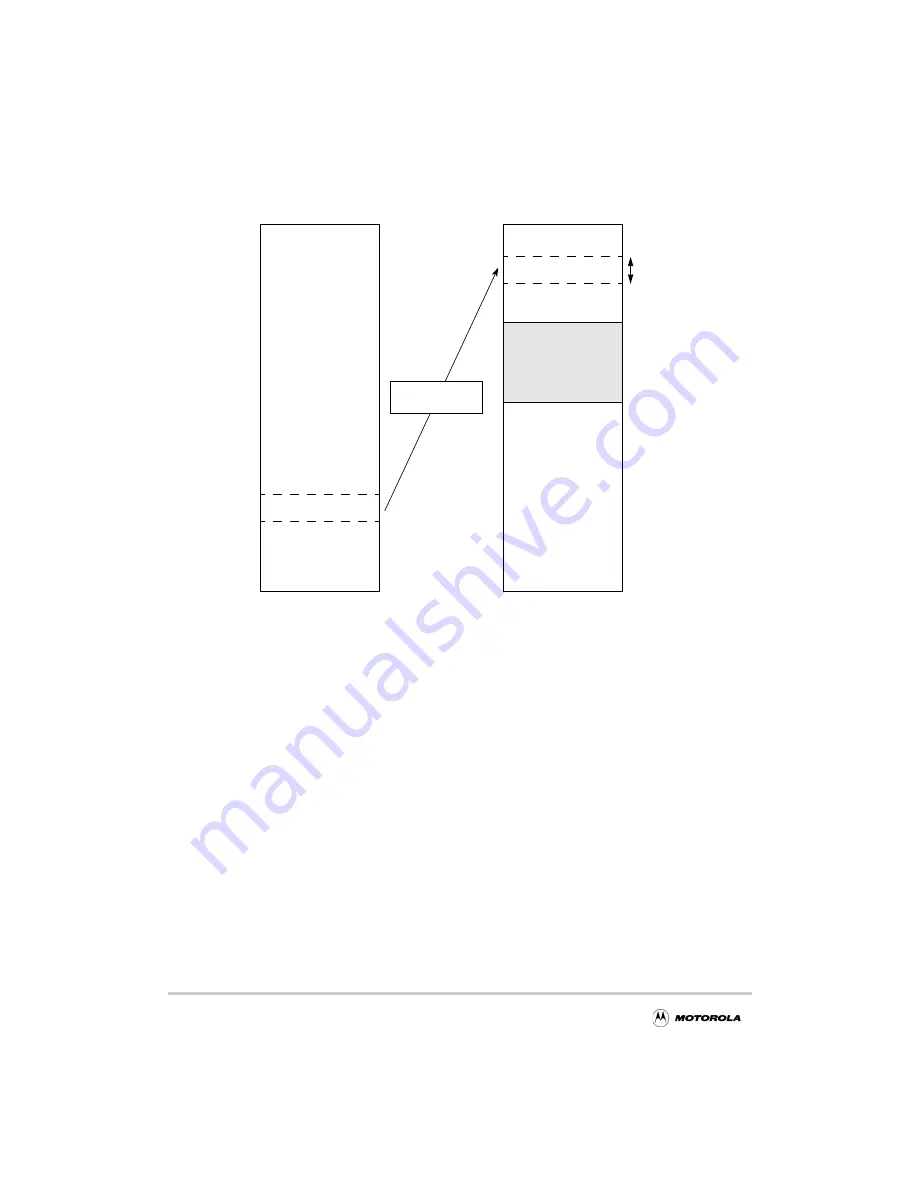

Figure 3-6. Inbound PCI Address Translation

Inbound address translation only allows address translation to the local memory space (the

lower 1 Gbyte of the address space). This means that an external PCI master cannot access

devices in the ROM/Port X address space when using inbound address translation. Since

the local memory space is restricted to addresses below 0x4000_0000 (1 Gbyte), any access

that gets translated above 0x4000_0000 triggers a memory select error. Thus, the entire

inbound translation window must be programmed to be below 0x4000_0000.

The local memory base address register (LMBAR) and the inbound translation window

register (ITWR) specify the location and size of the inbound memory window and the

inbound translation window. These registers are described in Section 3.3.3, “Address

Translation Registers.” Inbound address translation may be disabled by programming the

inbound window size in the ITWR to all zeros. If inbound translation is disabled, the

MPC8240 ignores all PCI memory transactions.

Note that overlapping the inbound memory window and the outbound translation window

is not supported and can cause unpredictable behavior. Also note that the inbound memory

window must not overlap the EUMB as specified by the PCSRBAR (PCI memory space

view). See Section 3.4, “Embedded Utilities Memory Block (EUMB),” for more

information.

Processor

PCI memory space

Local memory space

0

4G

0

4G

PCI Memory Space

Inbound memory

Local memory

Inbound translation

window

Inbound address

translation

base address

Inbound window

Inbound translation

2G

base address

window

size

1G

View

Core

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...