3-14

MPC8240 Integrated Processor User’s Manual

Address Translation

The outbound memory base address register (OMBAR) and the outbound translation

window register (OTWR) specify the location and size of the outbound memory window

and the outbound translation window. These registers are described in Section 3.3.3,

“Address Translation Registers.” Outbound address translation may be disabled by

programming the outbound window size to all zeros.

Note that overlapping the inbound memory window and the outbound translation window

is not supported and can cause unpredictable behavior. Also, the outbound memory window

and the outbound translation window must not overlap with the EUMB as specified by the

EUMBBAR (from the processor’s view) or the PCSRBAR (from the PCI memory space

view). Operation is not guaranteed if the two are overlapping.

3.3.3 Address Translation Registers

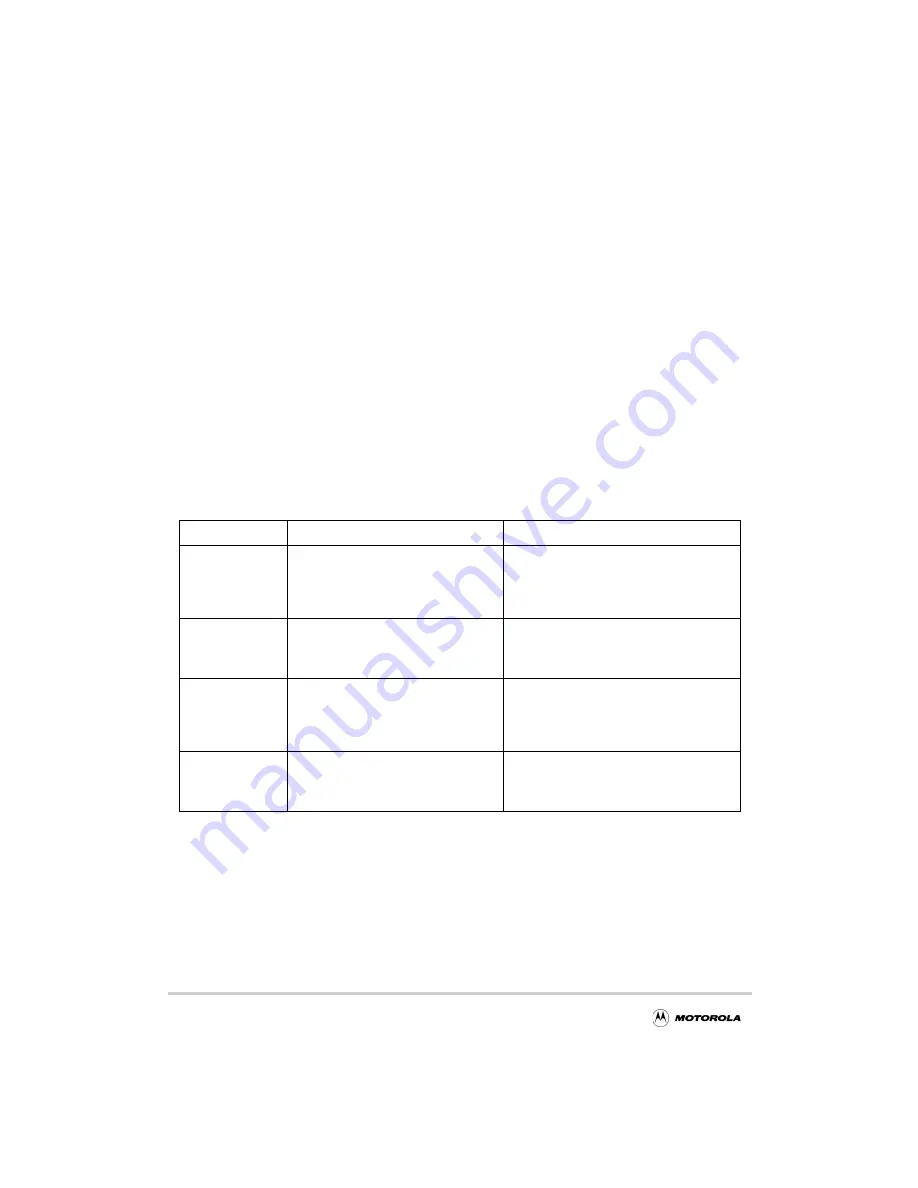

This section describes the address translation registers in detail. The address translation

registers, summarized in Table 3-7, specify the windows for inbound and outbound address

translation.

Table 3-7. ATU Register Summary

Register Name

Location

Description

Local memory base

address register

(LMBAR)

MPC8240 internal configuration

registers—see Chapter 4, “Configuration

Registers”

Offset 0x10

Specifies the starting address of the inbound

memory window. PCI memory transactions in

the inbound memory window are translated to

the inbound translation window (specified in the

ITWR) in local memory.

Inbound translation

window register

(ITWR)

EUMB—see Section 3.4, “Embedded

Utilities Memory Block (EUMB)”

Offset 0x0_2310 (local)

Offset 0x310 (PCI)

Specifies the starting address of the inbound

translation window and the size of the window.

Outbound memory

base address

register

(OMBAR)

EUMB—see Section 3.4, “Embedded

Utilities Memory Block (EUMB)”

Offset 0x0_2300 (local)

Offset 0x300 (PCI)

Specifies the starting address for the outbound

memory window. Processor transactions in the

outbound memory window are translated to the

outbound translation window (specified in the

OTWR) in PCI memory space.

Outbound

translation window

register

(OTWR)

EUMB—see Section 3.4, “Embedded

Utilities Memory Block (EUMB)”

Offset 0x0_2308 (local)

Offset 0x308 (PCI)

Specifies the starting address of the outbound

translation window and the size of the window.

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...