4-10

MPC8240 Integrated Processor User’s Manual

PCI Interface Configuration Registers

.

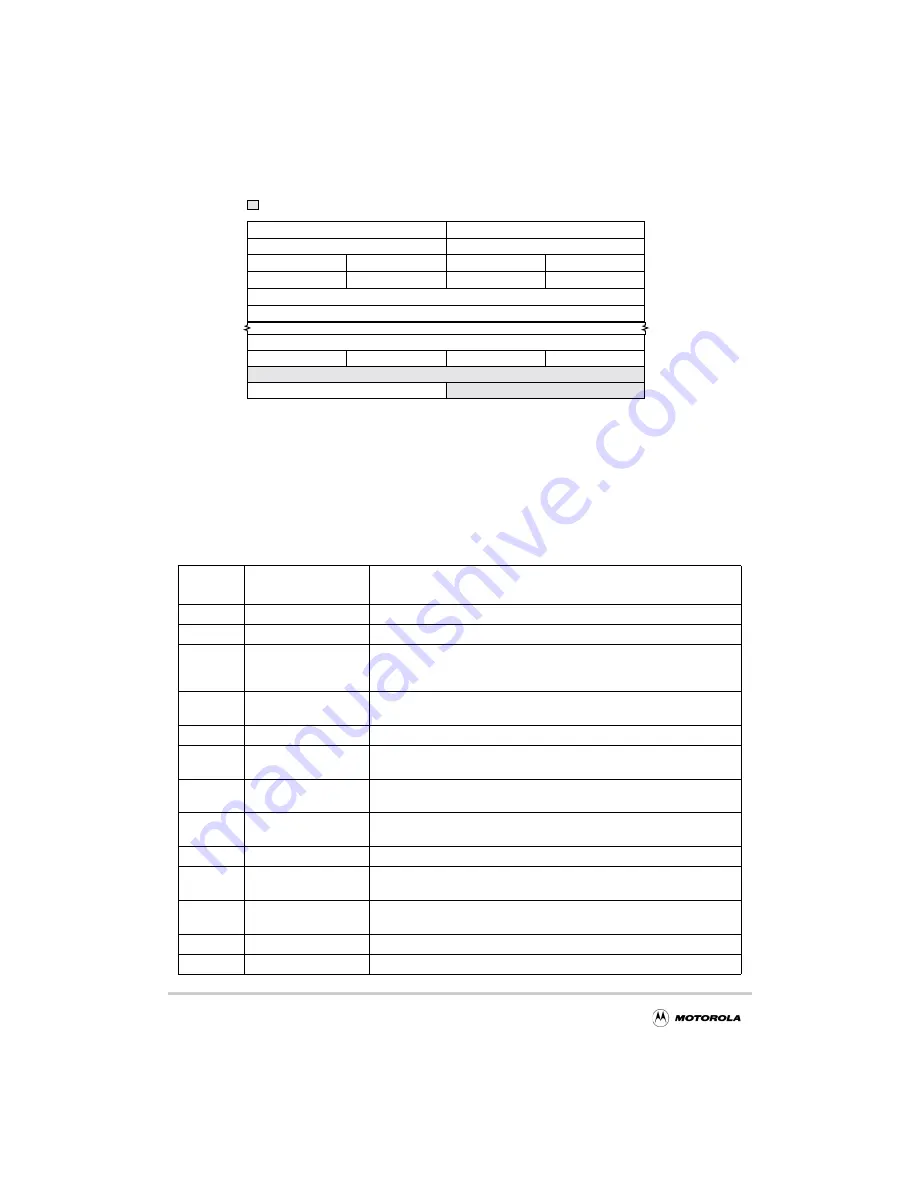

Figure 4-2. PCI Accessible Configuration Space

4.2 PCI Interface Configuration Registers

The PCI Local Bus Specification defines the configuration registers from 0x00 through

0x3F. Table 4-4 summarizes the PCI configuration registers of the MPC8240. Detailed

descriptions of these registers are provided in the PCI Local Bus Specification.

Table 4-4. PCI Configuration Space Header Summary

Address

Offset

Register Name

Description

0x00

Vendor ID

Identifies the manufacturer of the device (0x1057 = Motorola)

0x02

Device ID

Identifies the particular device (0x0003 = MPC8240)

0x04

PCI command

Provides coarse control over a device’s ability to generate and respond to

PCI bus cycles (see Section 4.2.1, “PCI Command Register—Offset 0x04,”

for more information)

0x06

PCI status

Records status information for PCI bus-related events (see Section 4.2.2,

“PCI Status Register—Offset 0x06,” for more information)

0x08

Revision ID

Specifies a device-specific revision code (assigned by Motorola)

0x09

Standard programming

interface

Identifies the register-level programming interface

of the MPC8240 (0x00)

0x0A

Subclass code

Identifies more specifically the function of the MPC8240

(0x00 = host bridge)

0x0B

Base class code

Broadly classifies the type of function the MPC8240 performs

(0x06 = bridge device)

0x0C

Cache line size

Specifies the system cache line size

0x0D

Latency timer

Specifies the value of the latency timer for this bus master in PCI bus clock

units

0x0E

Header type

Bits 0–6 identify the layout of bytes 10–3F; bit 7 indicates a multifunction

device. The MPC8240 uses the most common header type (0x00).

0x0F

BIST control

Optional register for control and status of built-in self test (BIST)

0x10–0x2F

—

Reserved on the MPC8240

Reserved

Device ID (0x0003)

Vendor ID (0x1057)

PCI Status

PCI Command

Class Code

Standard Programming

Subclass Code

Revision ID

BIST Control

Latency Timer

Header Type

Cache Line Size

MAX LAT

Interrupt Pin

MIN GNT

Interrupt Line

00

04

08

0C

3C

Address

Offset (Hex)

Local Memory Base Address Register

10

Peripheral Control and Status Registers Base Address Register

14

40

44

/ / / / / / / /

PCI Arbiter Control

/ / / / / / / /

Expansion ROM Base Address

30

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...