Chapter 4. Configuration Registers

4-41

Address Map B Options Register—0xE0

4.9 Address Map B Options Register—0xE0

The address map B options register (AMBOR) controls various configuration settings that

can be used to alias some addresses and to control accesses to holes in the address map.

Unrelated to address map B, there is also a bit that controls the operation of the DLL. See

Section 3.3.2, “DLL Operation and Locking,” for more information about operation of the

DLL.

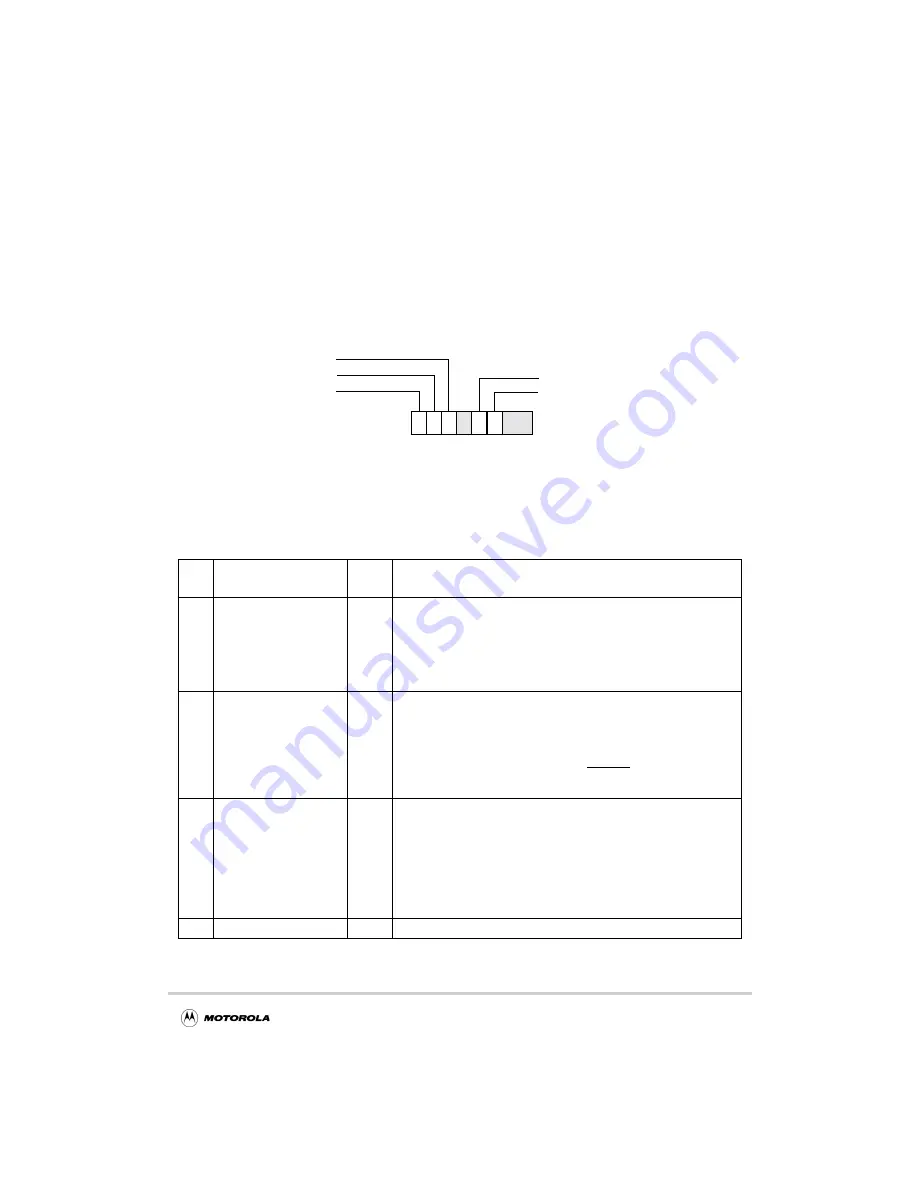

Figure 4-28 shows the bits of the AMBOR.

Figure 4-28. Address Map B Options Register (AMBOR)—0xE0

Table 4-37 shows the specific bit settings for the AMBOR.

Table 4-37. Bit Settings for the AMBOR—0xE0

Bits

Name

Reset

Value

Description

7

CPU_FD_ALIAS_EN

1

Used to direct processor accesses to addresses that begin with

0xFDxx_xxxx. This bit is used only for address map B (and not

supported in agent mode).

0 Access are routed normally

1 Processor accesses with 0xFDxx_xxxx address are forwarded to the

PCI bus as PCI memory accesses to 0x00xx_xxxx.

6

PCI_FD_ALIAS_EN

1

Used to direct processor responses to addresses that begin with

0xFDxx_xxxx. This bit is used only for address map B (and not

supported in agent mode).

0 No response

1 The MPC8240, as a PCI target, responds to addresses in the range

0xFD00_0000–0xFDFF_FFFF (asserts DEVSEL), and forwards the

transaction to system memory as 0x0000_0000–0x00FF_FFFF.

5

DLL_RESET

0

Used to reset the DLL tap point. See Section 3.3.2, “DLL Operation and

Locking.” This bit must be explicitly set and then cleared by software

during initialization in order to guarantee correct operation of the DLL

and the SDRAM_CLK[0:3] signals (if they are used)

0 DLL tries to lock the phase between the SDRAM_SYNC_IN signal

and the internal sys_logic_clk signal.

1 The SDRAM_CLK signals are driven from tap point 0 of the internal

delay line.

4

—

0

Reserved

0

0 0

7

6

5

4

3

2

1

0

CPU_FD_ALIAS_EN

PCI_FD_ALIAS_EN

DLL_RESET

PROC_COMPATIBILITY_HOLE

PCI_COMPATIBILITY_HOLE

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...