Chapter 5. PowerPC Processor Core

5-17

Programming Model

Table 5-3 shows the bit definitions for HID1.

5.3.1.2.3 Hardware Implementation-Dependent Register 2 (HID2)

The processor core implements an additional hardware implementation-dependent register

as shown in Figure 5-5, not described in the MPC603e User’s Manual.

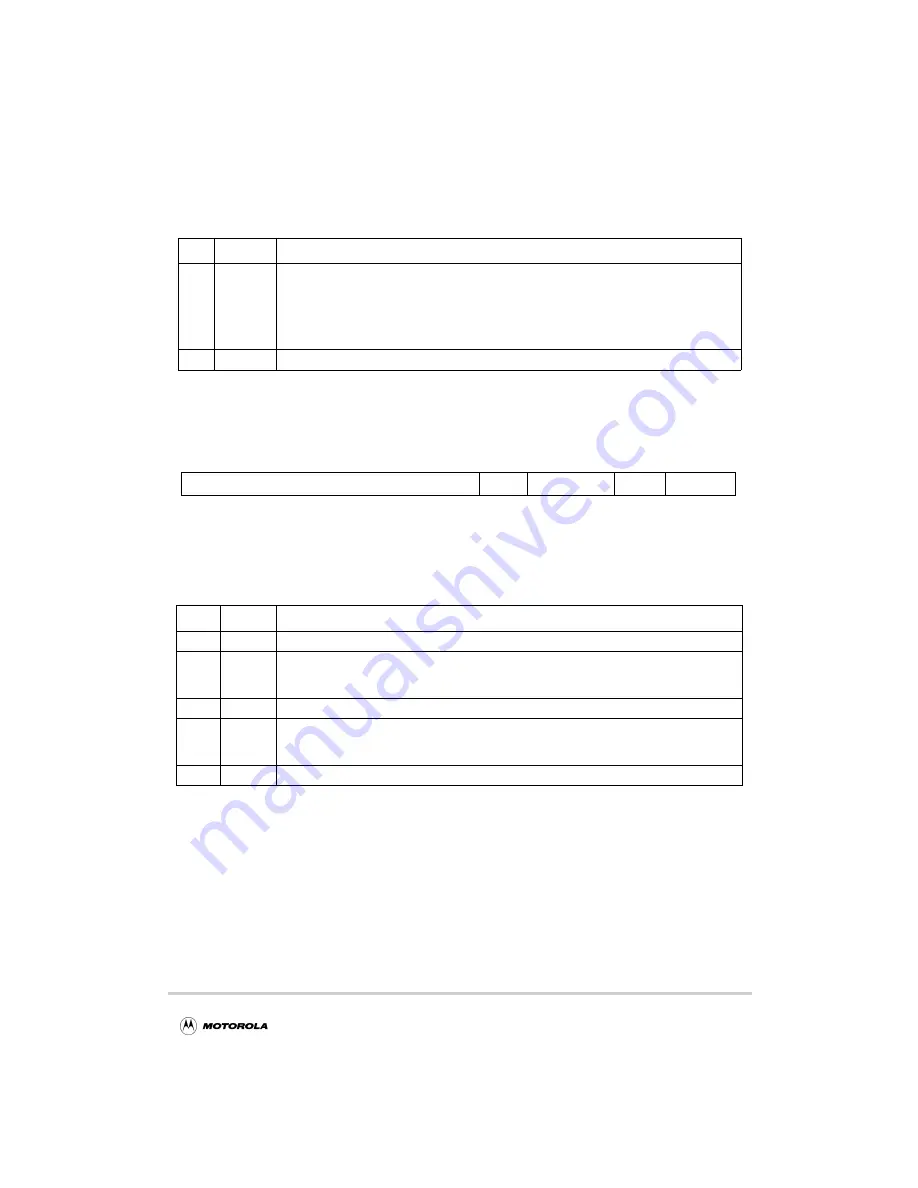

Figure 5-5. Hardware Implementation-Dependent Register 2 (HID2)

Table 5-4 describes the HID2 fields.

5.3.1.2.4 Processor Version Register (PVR)

Software can identify the MPC8240’s processor core by reading the processor version

register (PVR). The MPC8240’s processor version number is 0x0081; the processor

revision level starts at 0x0100 and is incremented for each revision of the chip. This

information is useful for data cache flushing routines for identifying the size of the cache

and identifying this processor as one that supports cache locking.

Table 5-3. HID1 Field Descriptions

Bits

Name

Function

0–4

PLLRATIO

PLL configuration processor core frequency ratio—This read-only field is determined by the

value on the PLL_CFG[0–4] signals during reset and the processor-to-memory clock frequency

ratio defined by that PLL_CFG[0–4] value. See MPC8240 Hardware Specification for a listing of

supported settings. Note that multiple settings of the PLL_CFG[0–4] signals can map to the

same PLLRATIO value. Thus, system software cannot read the PLLRATIO value and associate

it with a unique PLL_CFG[0–4] value.

5–31

—

Reserved

Table 5-4. HID2 Field Descriptions

Bits

Name

Function

0–15

—

Reserved

16–18

IWLCK

Instruction cache way lock—Useful for locking blocks of instructions into the instruction cache for

time-critical applications where deterministic behavior is required. Refer to Section 5.4.2.3,

“Cache Locking,” for more information.

19–23

—

Reserved

24–26

DWLCK

Data cache way lock—Useful for locking blocks of data into the data cache for time-critical

applications where deterministic behavior is required. Refer to Section 5.4.2.3, “Cache Locking,”

for more information.

27–31

—

Reserved

0

15

16

18 19

23 24

26 27

31

IWLCK

DWLCK

—

—

—

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...