Chapter 6. MPC8240 Memory Interface

6-33

SDRAM Interface Operation

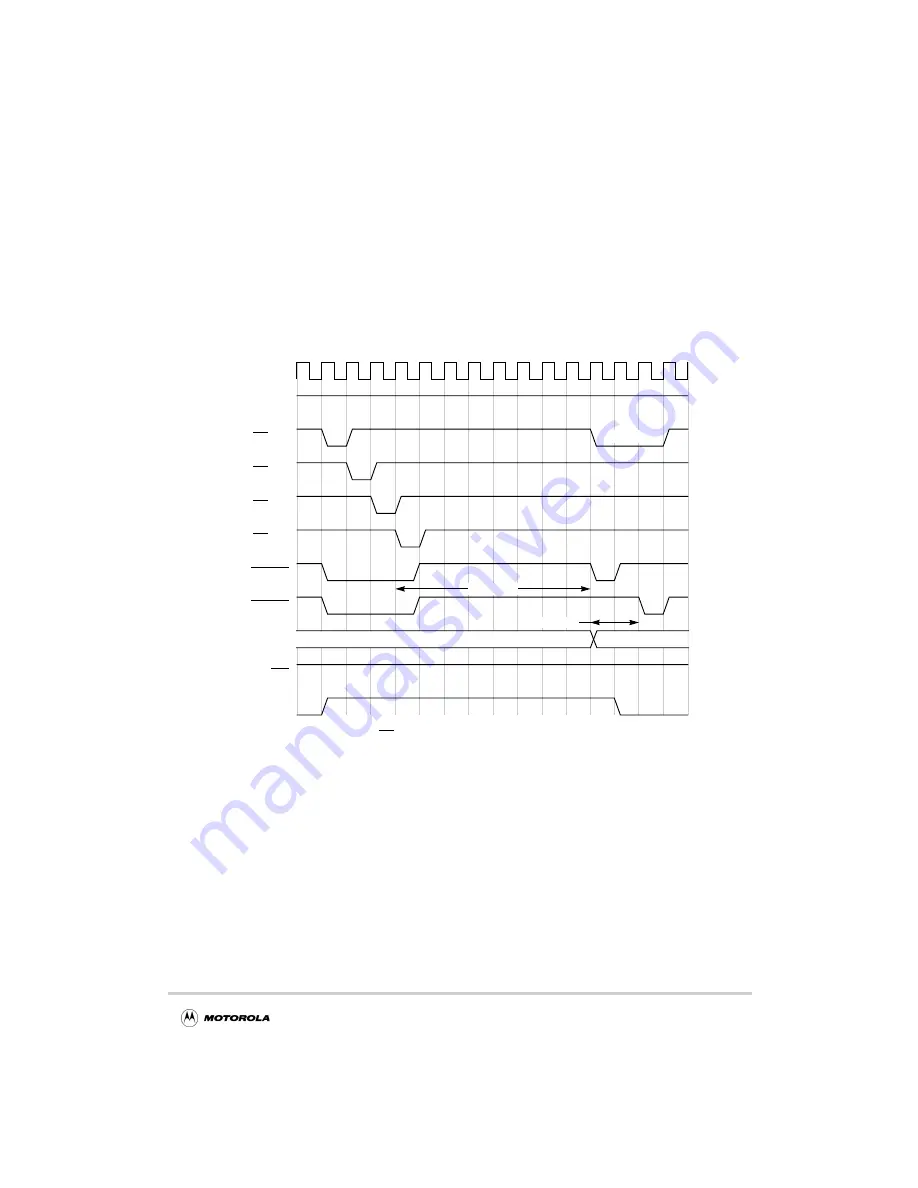

6.2.12.1 SDRAM Refresh Timing

The CBR refresh timing for SDRAM is controlled by the programmable timing parameter

MCCR3[REFREC]. REFREC represents the number of clock cycles from the refresh

command until a bank-activate command is allowed. The AC specifications of the specific

SDRAM device provides a minimum refresh-to-activate interval.

The MPC8240 implements bank staggering for CBR refreshes, as shown in Figure 6-18.

This reduces instantaneous current consumption for memory refresh operations.

Figure 6-18. SDRAM Bank Staggered CBR Refresh Timing

6.2.12.2 SDRAM Refresh and Power Saving Modes

The MPC8240’s memory interface provides for sleep, doze, and nap power saving modes

defined for the local processor architecture. See Chapter 14, “Power Management,” for

more information on these modes.

In doze and nap power saving modes, the MPC8240 supplies normal CBR refresh to

SDRAM. In sleep mode, the MPC8240 can be configured to use the SDRAM self-refresh

mode, provide normal refresh to SDRAM, or provide no refresh support. If the MPC8240

is configured to provide no refresh support in sleep mode, system software is responsible

for appropriately preserving SDRAM data, such as by copying to disk. Table 6-14

summarizes the MPC8240configuration bits relevant to power-saving modes.

SDRAM

CKE

CS[0,7]

CS[1,6]

CS[2,5]

SDRAS

CS[3,4]

SDCAS

ACTORW

NOTE: Only one CS signal is asserted for the bank-activate and read commands.

CLK[0:3]

WE

DQM[0:7]

ROW ADDR

COL ADDR

SDBA0

SDMA[12:0]

REFREC

* See note

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...