9-6

MPC8240 Integrated Processor User’s Manual

I

2

O Interface

9.3.3 FIFO Descriptions

There are two paths for messages—an inbound queue to receive messages from the remote

host (and other IOPs) and an outbound queue to pass messages to a remote host. Each queue

is implemented as a pair of FIFOs. The inbound and outbound message queues each

consists of a free_list FIFO and a post_list FIFO.

Messages are comprised of frames that are at least 64 bytes long. The message frame

address (MFA) points to the first byte of the message frame. The messages are located in a

pool of system memory (any memory address accessible through the PCI bus). Tracking of

the status and location of these messages is done with the four FIFOs that are located in

local memory. One FIFO in each queue tracks the free MFAs (free_list FIFO). The other

FIFO tracks the MFAs that have posted messages (post_list FIFO). These FIFOs are

managed by the remote processors and the processor core through the MPC8240 I

2

O

registers. For more information, see Section 9.3.2, “I2O Register Summary”.

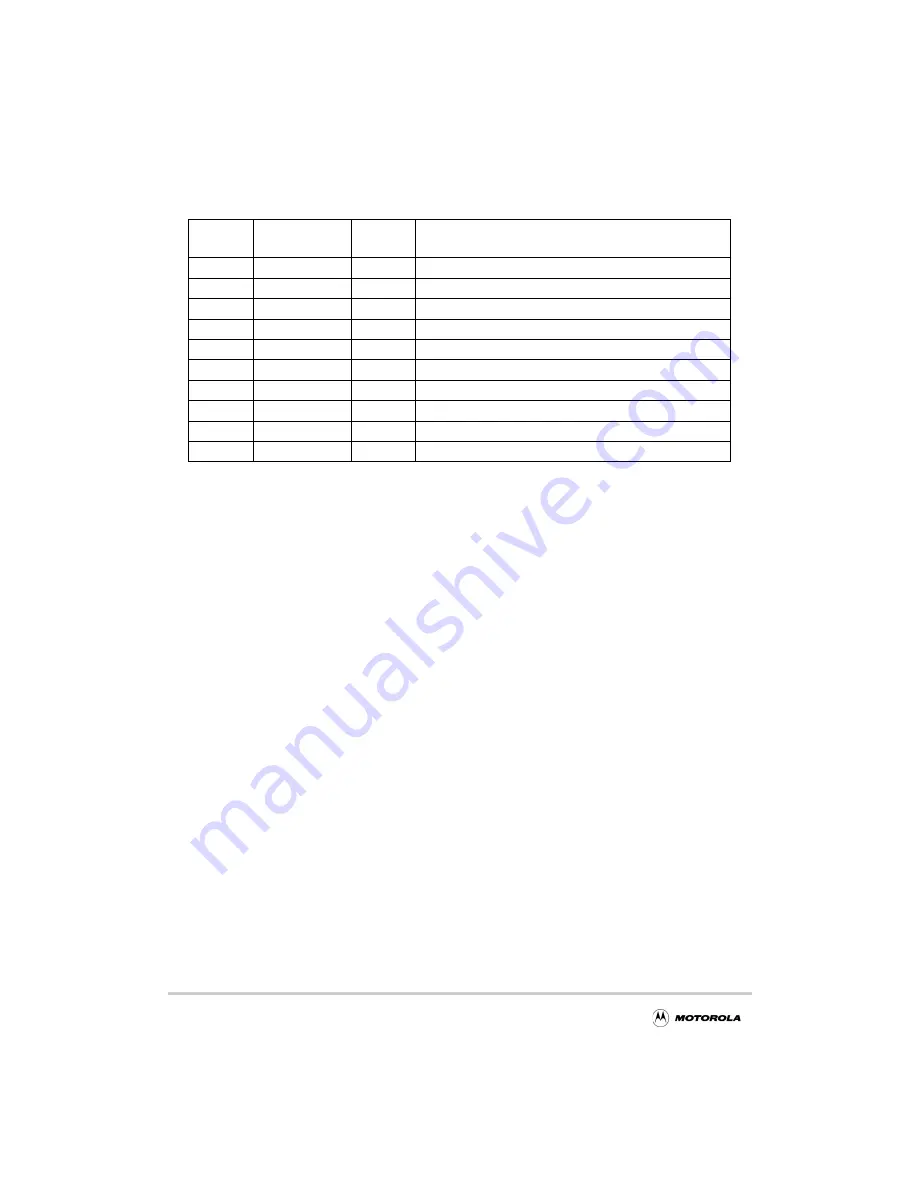

—

0x0_0120

IFHPR

Inbound free_FIFO head pointer register

—

0x0_0128

IFTPR

Inbound free_FIFO tail pointer register

—

0x0_0130

IPHPR

Inbound post_FIFO head pointer register

—

0x0_0138

IPTPR

Inbound post_FIFO tail pointer register

—

0x0_0140

OFHPR

Outbound free_FIFO head pointer register

—

0x0_0148

OFTPR

Outbound free_FIFO tail pointer register

—

0x0_0150

OPHPR

Outbound post_FIFO head pointer register

—

0x0_0158

OPTPR

Outbound post_FIFO tail pointer register

—

0x0_0164

MUCR

Messaging unit control register

—

0x0_0170

QBAR

Queue base address register. Must be set on 1-Mbyte boundary

Table 9-7. I

2

O Register Summary (Continued)

PCI Offset

Local Memory

Offset

Acronym

Name

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...