11-16

MPC8240 Integrated Processor User’s Manual

Register Definitions

11.9 Register Definitions

The following sections describe the registers of the EPIC unit.

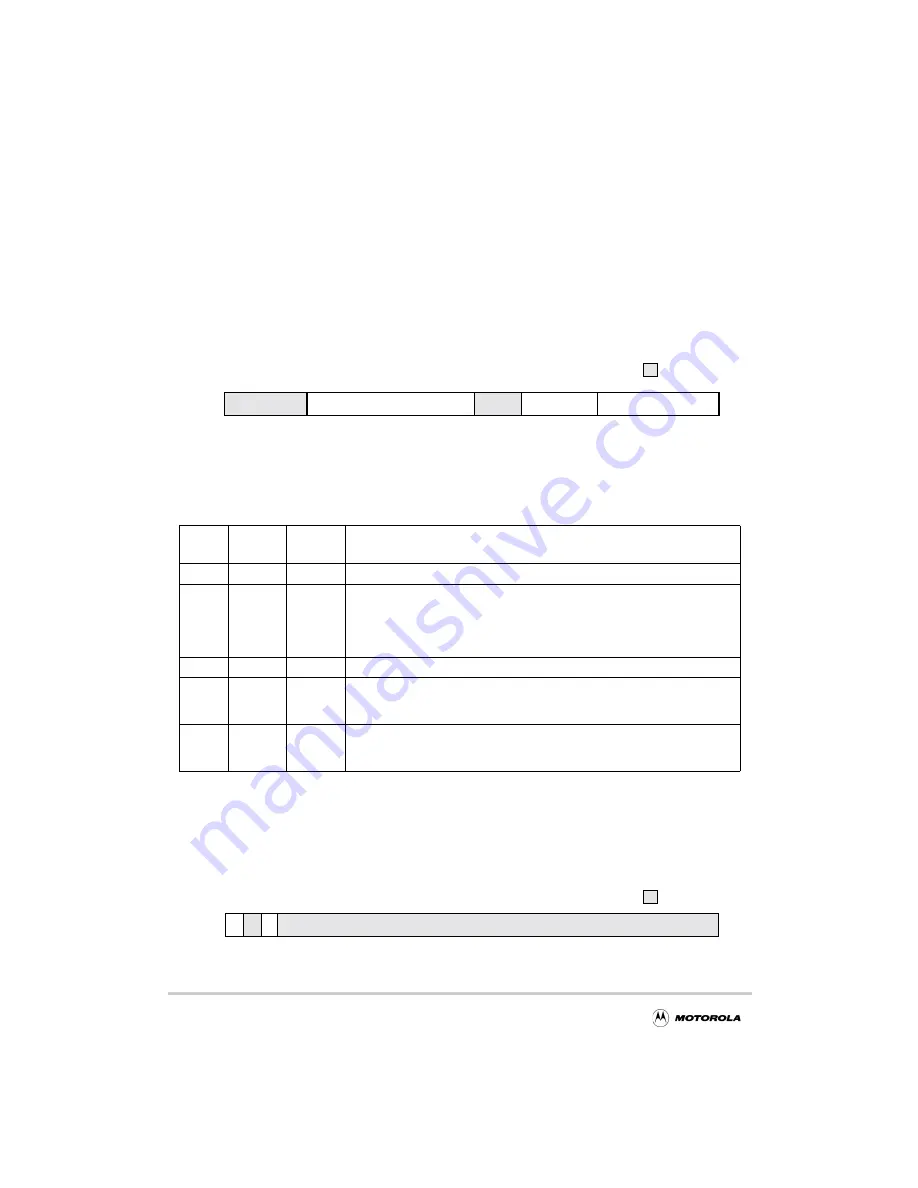

11.9.1 Feature Reporting Register (FRR)

The feature reporting register (FRR) provides information about the interrupt and processor

configurations. It also contains controller version information. Note that this register is

read-only. Figure 11-4 shows the bits in the FRR.

Figure 11-4. Feature Reporting Register (FRR)

Table 11-5 describes the bit settings for the FRR.

11.9.2 Global Configuration Register (GCR)

The GCR provides programming control for resetting the EPIC unit and for setting the

external interrupts mode. Note that this register is read/write. Figure 11-5 shows the bits in

the GCR.

Figure 11-5. Global Configuration Register (GCR)

Table 11-5. FRR Field Descriptions—Offset 0x4_1000

Bits

Name

Reset

Value

Description

31–27

—

All 0s

Reserved

26–16

NIRQ

0x017

Number of interrupts. This field contains the maximum number of interrupt

sources supported. In the MPC8240, there are a maximum of 24 interrupts in use

at one time: the 4 internal sources (I

2

C, DMA (2), and MU), 4 timer sources and

16 external sources. A zero in this field corresponds to one interrupt, and so on.

Thus the value of 0x017 corresponds to 24 interrupts.

15–13

—

All 0s

Reserved

12–8

NCPU

0x00

Number of CPUs. This field contains the number of the highest CPU supported.

Because one CPU is supported by the MPC8240’s EPIC unit, the value is zero

corresponding to CPU 0.

7–0

VID

0x02

Version ID for this interrupt controller. This value reports the level of OpenPIC

specification supported by this implementation. VID =2, representing version

level 1.2 of OpenPIC, for the initial release of the MPC8240.

0 0 0 0 0

NIRQ

0 0 0

NCPU

VID

31

27 26

16 15

13 12

8

7

0

Reserved

R

0 M

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

31 30 29 28

0

Reserved

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...