Chapter 11. Embedded Programmable Interrupt Controller (EPIC) Unit

11-21

Register Definitions

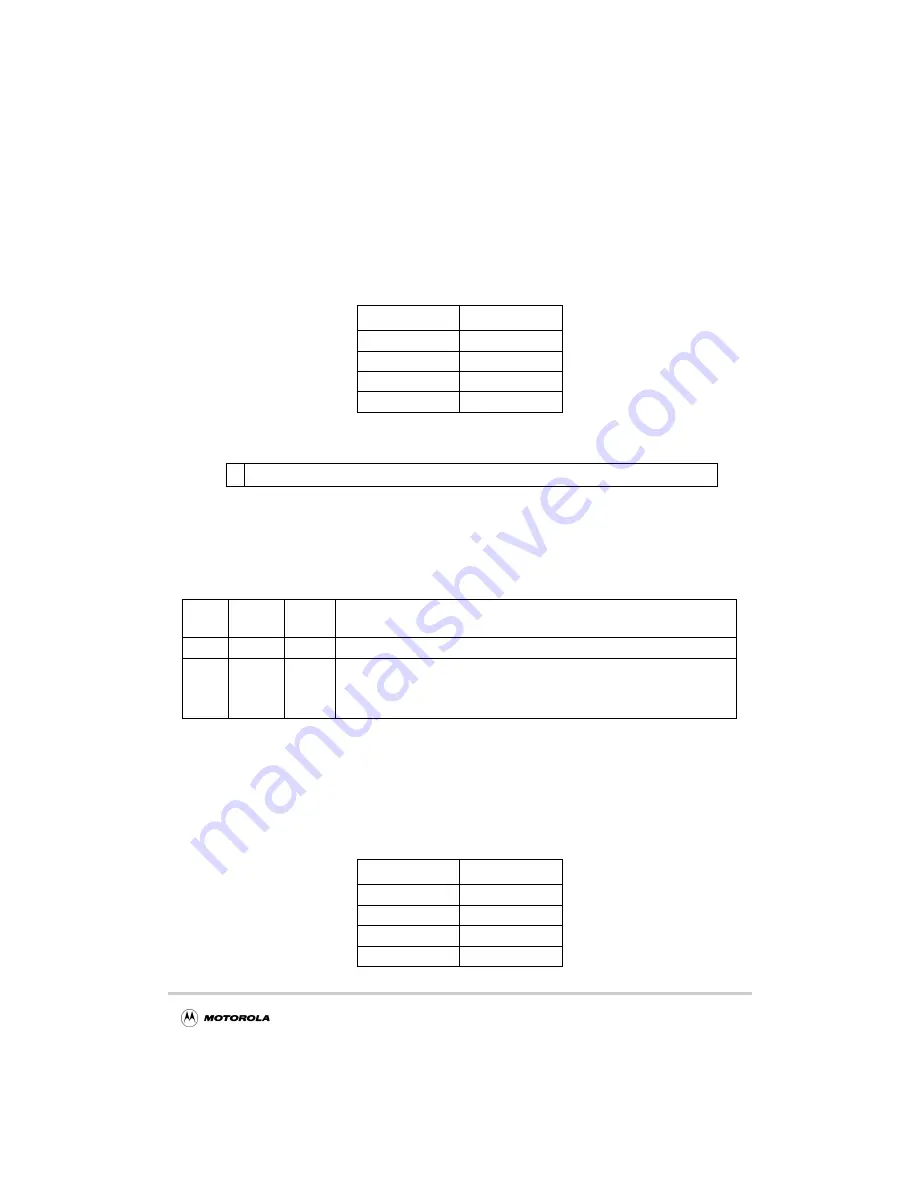

11.9.7.2 Global Timer Current Count Registers (GTCCRs)

The GTCRRs contain the current count for each of the four EPIC timers. Note that these

registers are read-only. The address offsets from EUMBBAR for the GTCCRs are

described in Table 11-12.

Figure 11-11 shows the bits of the GTCCRs.

Figure 11-11. Global Timer Current Count Register (GTCCR)

Table 11-13 describes the bit settings for the GTCCRs.

11.9.7.3 Global Timer Base Count Registers (GTBCRs)

The GTBCRs contain the base count for each of the four EPIC timers. This is the value

reloaded into the GTCCRs when they count down to zero. Note that these registers are

read/write. The address offsets from EUMBBAR for the GTBCRs are described in

Table 11-14.

Table 11-12. EUMBBAR Offsets for GTCCRs

GTCCR

Offset

GTCCR0

0x4 _1100

GTCCR1

0x4_1140

GTCCR2

0x4_1180

GTCCR3

0x4_11C0

Table 11-13. GTCCR Field Descriptions

Bits

Name

Reset

Value

Description

31

T

0

Toggle. This bit toggles whenever the current count decrements to zero.

30–0

COUNT

All 0s

Current timer count. This 31-bit field is decremented while the GTBCR[CI] bit is

zero. When the timer counts down to zero, this field is reloaded from the base

count register, the toggle bit is inverted, and an interrupt is generated (provided it

is not masked).

Table 11-14. EUMBBAR Offsets for GTBCRs

GTBCR

Offset

GTBCR0

0x4_1110

GTBCR1

0x4_1150

GTBCR2

0x4_1190

GTBCR3

0x4_11D0

T

COUNT

31 30

0

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...