Chapter 15. Debug Features

15-17

Memory Data Path Error Injection/Capture

15.5 Memory Data Path Error Injection/Capture

The MPC8240 provides hardware to exercise and debug the on-chip ECC and parity logic

by allowing the user to inject multi-bit stuck-at faults onto the peripheral logic or memory

data/parity buses and to capture the data/parity upon the receipt of an ECC or parity error.

The memory data path error injection/capture system is programmed via the six memory

data path diagnostic registers. These registers allow the user to program error injection

masks and to monitor ECC/parity error capture data. The memory data path diagnostic

registers are accessible from either the local bus or PCI port. All memory data path

diagnostic registers are reset to zero, 0x0000_0000, unless otherwise specified.

15.5.1 Memory Data Path Error Injection Mask Registers

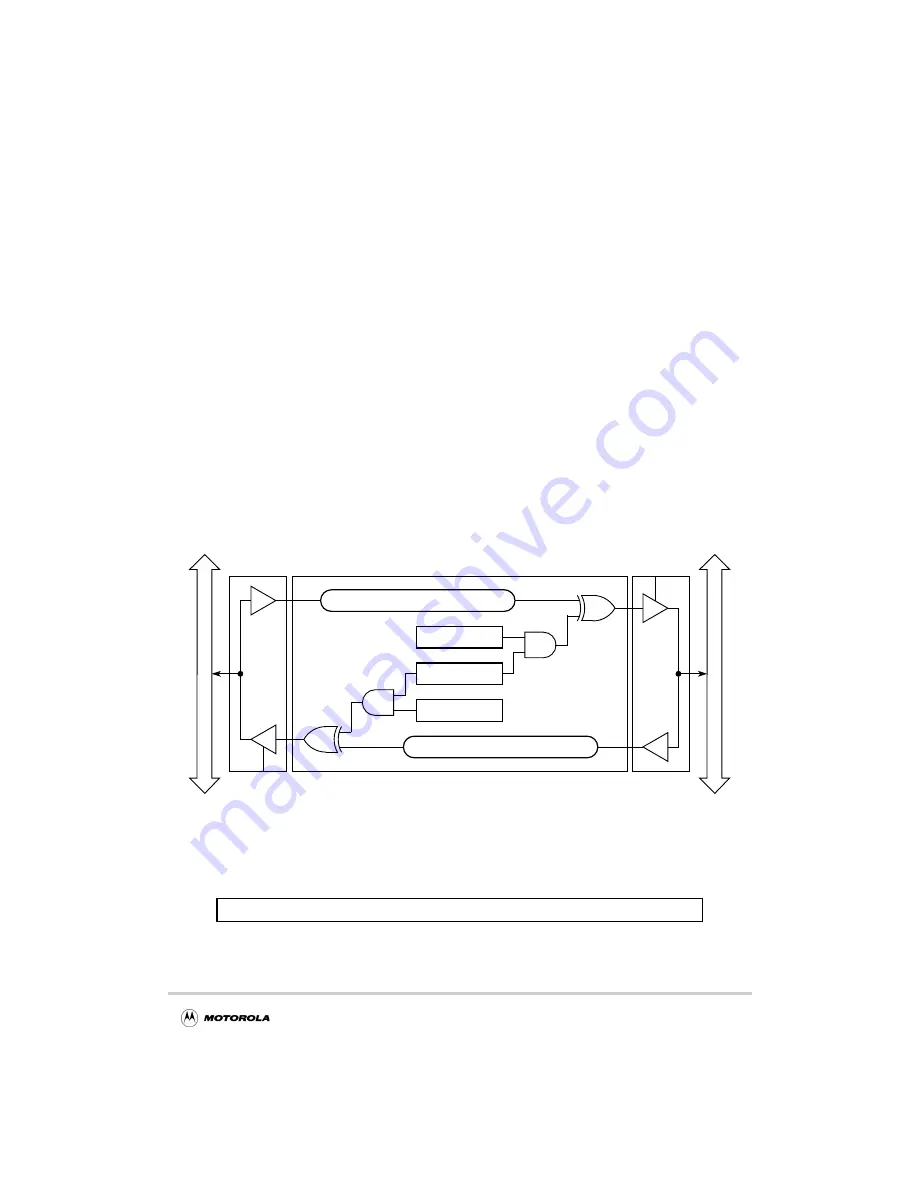

The memory data path error injection masks are used to inject errors onto the internal

peripheral logic bus or the memory data/parity buses as shown in Figure 15-23. Separate

mask registers are provided for the high data, low data, and parity buses. The masks are

bit-wise inverting; a 0b1 in the mask causes the corresponding bit on the data/parity bus to

be inverted. The masks are applied to the read and/or write data path by read and write mask

enable bits. These registers can be read or written and are initialized to 0x0000_0000.

Figure 15-17. Functional Diagram of Memory Data Path Error Injection

15.5.1.1 DH Error Injection Mask Register

Figure 15-18 shows the bits of the DH error injection mask register.

Figure 15-18. DH Error Injection Mask (MDP_ERR_INJ_MASK_DH)—

Offsets 0xF_F000, 0xF00

Programmable data path w/ECC

P

e

ripher

al Logic Bus

Write_enable

Data_mask

Programmable data path w/ECC

Read_enable

Memor

y Bus

DH[31:0]

31

0

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...