ISD91200 Series Technical Reference Manual

Release Date: Sep 16, 2019

- 413 -

Revision 2.4

7

6

5

4

3

2

1

0

Reserved

LVL

Table 7-10

Microphone Bias Voltage Level Selection

Register (ANA_, address 0x4008_0028).

Bits

Description

[31:3]

Reserved

Reserved.

[2:0]

LVL

LVL

controls the voltage output of the MICBIAS generator, voltages are encoded

as following:

0 - 1.5V

1 - 1.8V

2 - 1.95V

3 - 2.1V

4 - 2.25V

5 - 2.4V

6 - 2.55V

7 - 2.7

Note:

MICBIAS voltage should be at least 300mV lower than VCCA.

7.4.7

Oscillator Frequency Measurement and Control

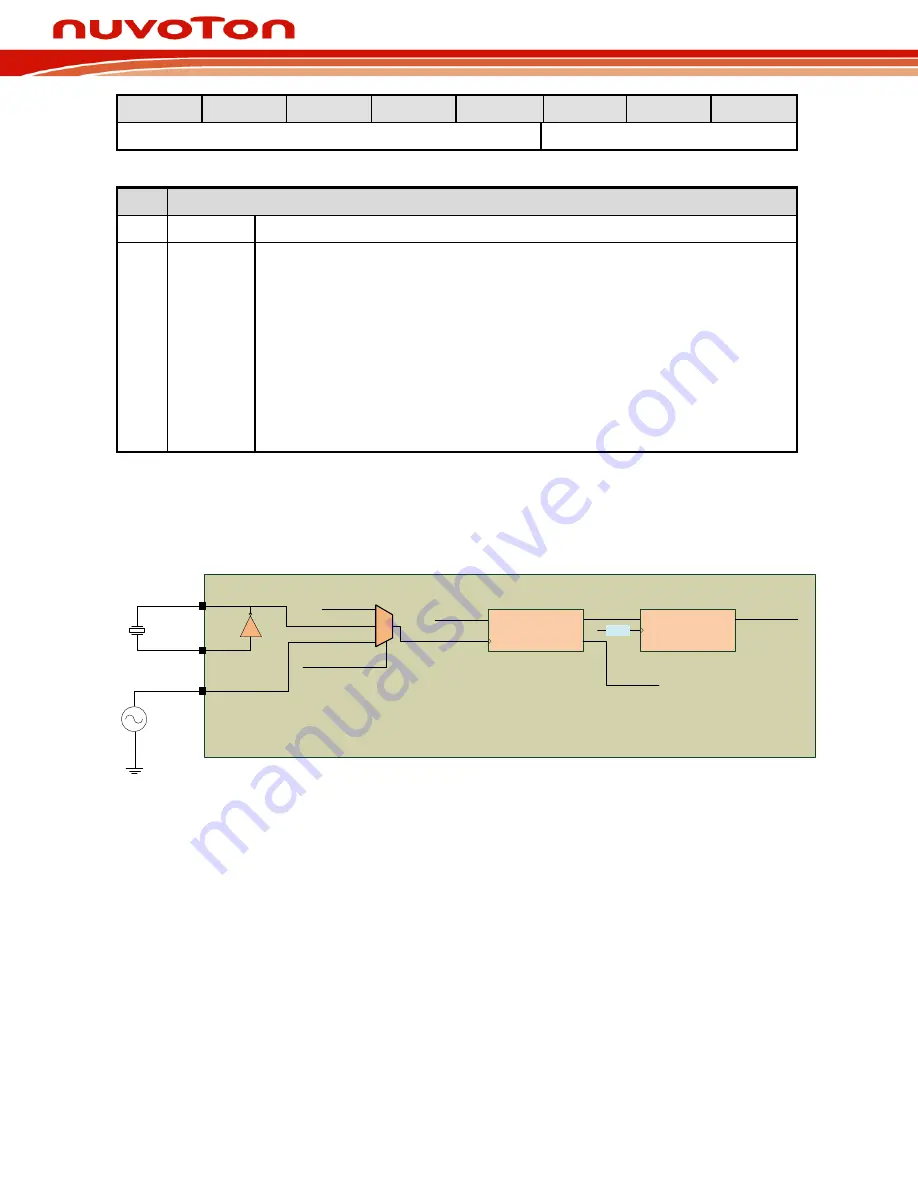

The ISD91200 provides a functional unit that can be used to measure PCLK frequency given a reference frequency

such as the 32.768kHz crystal or an I2S frame synchronization signal. This is simply a special purpose timer/counter

as shown in Figure 7-8 Oscillator Frequency Measurement Block Diagram.

I2S_WS

X032K

Counter

16 bits

PCLK

EN

FREQ_CNT[15:0]

FM_DONE

FM_SEL[1:0]

XI32K

OSC32K

M

U

X

OSC16K

CYCLE_CNT

8 bits

FM_CYCLE[7:0]

Figure 7-8 Oscillator Frequency Measurement Block Diagram

The block can be used to trim/measure the internal high frequency oscillator to the reference frequency of the

32.768kHz oscillator or an external reference frequency fed in on the I2S frame sync input. With this the internal clock

can be set at arbitrary frequencies, other than those trimmed at manufacturing, or can be periodically trimmed to

account for temperature variation. The block can also be used to measure the 10kHz oscillator frequency relative to

the internal master oscillator.

An example of use would be to measure the internal oscillator with reference to the 32768Hz crystal. To do this:

CLK_APBCLK0.ANACKEN = 1; /* Turn on analog peripheral clock */

ANA_FQMMCTL.CLKSEL = 1; // Select reference source as 32kHz XTAL input

ANA_FQMMCTL.CYCLESEL = DRVOSC_NUM_CYCLES-1;