ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

242

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

6.5.5

Functional Description

6.5.5.1

Input Mode

Writing 0b00 into MODEn bits (Px_MODE[2n+1:2n]) puts the corresponding Px.n pin in Input mode,

and the pin will be in tri-state (high impedance). The input pin’s status is reflected in PX PIN[n] bit.

For example if PA.0 is an input pin, the input level can be read by reading PA_PIN register, and

PA_PIN[0] has the input value for PA.0 pin.

6.5.5.2

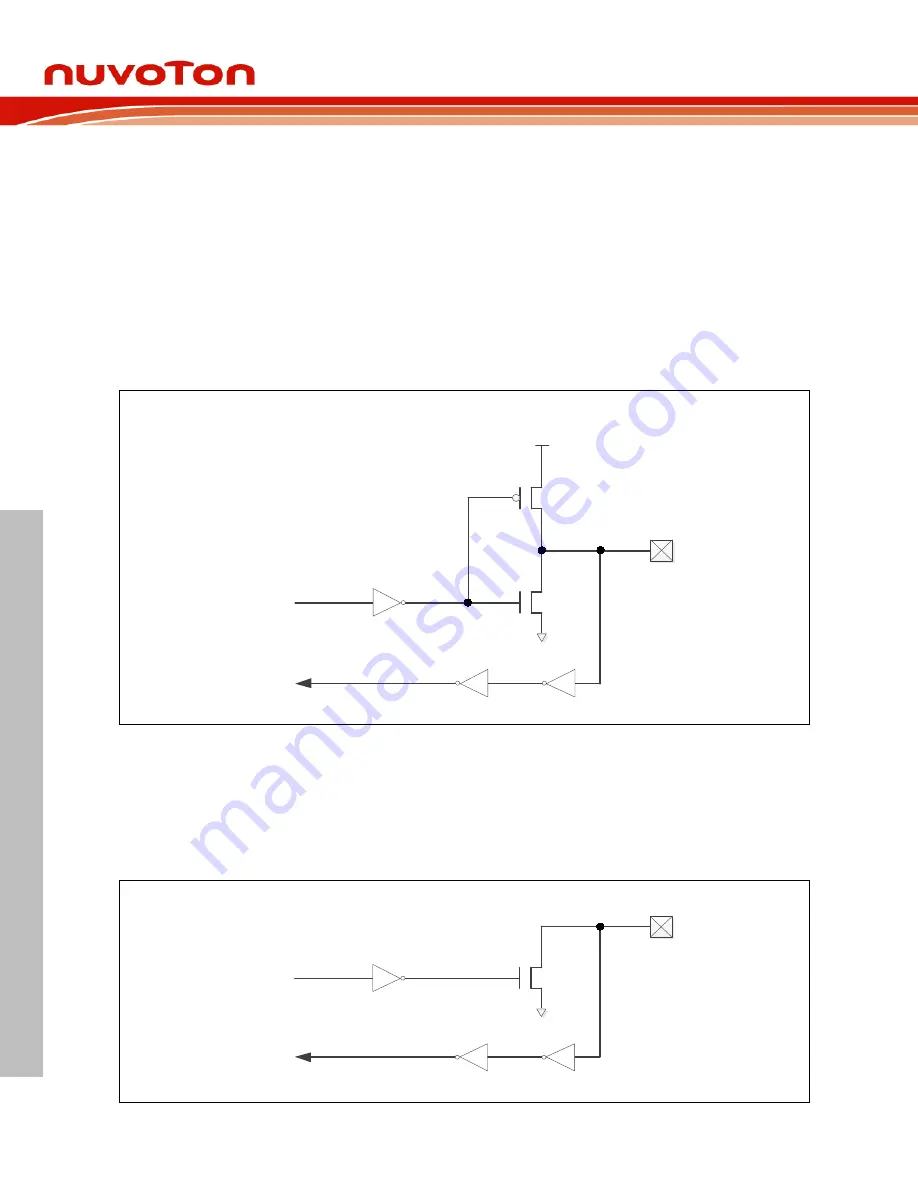

Push-pull Output Mode

Writing 0b01 into MODEn bits (Px_MODE[2n+1:2n]) puts the corresponding Px.n pin in in Push-

pull Output mode, and the pin supports digital output function with source/sink current capability.

As shown in Figure 6.5-2, the bit value in the corresponding DOUT (Px_DOUT[n]) is driven on the

pin.

Port Pin

Port Pin

N

N

P

P

VDD

VDD

Port Latch Data

Port Latch Data

Input Data

Input Data

Figure 6.5-2 Push-Pull Output

6.5.5.3

Open-drain Mode

Writing 0b10 to MODEn bits (Px_MODE[2n+1:2n]) configures the corresponding Px.n pin as Open-

drain mode I/O pin. External pull-up register is required to drive high state. If DOUT (Px_DOUT[n])

bit is 0, the pin drives low. If DOUT (Px_DOUT[n]) bit is 1, the pin drives high assuming there is

external pull high.

Open-drain Mode I/O function is shown in Figure 6.5-3.

Port Pin

Port Pin

N

N

Port Latch Data

Port Latch Data

Input Data

Input Data