ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

546

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

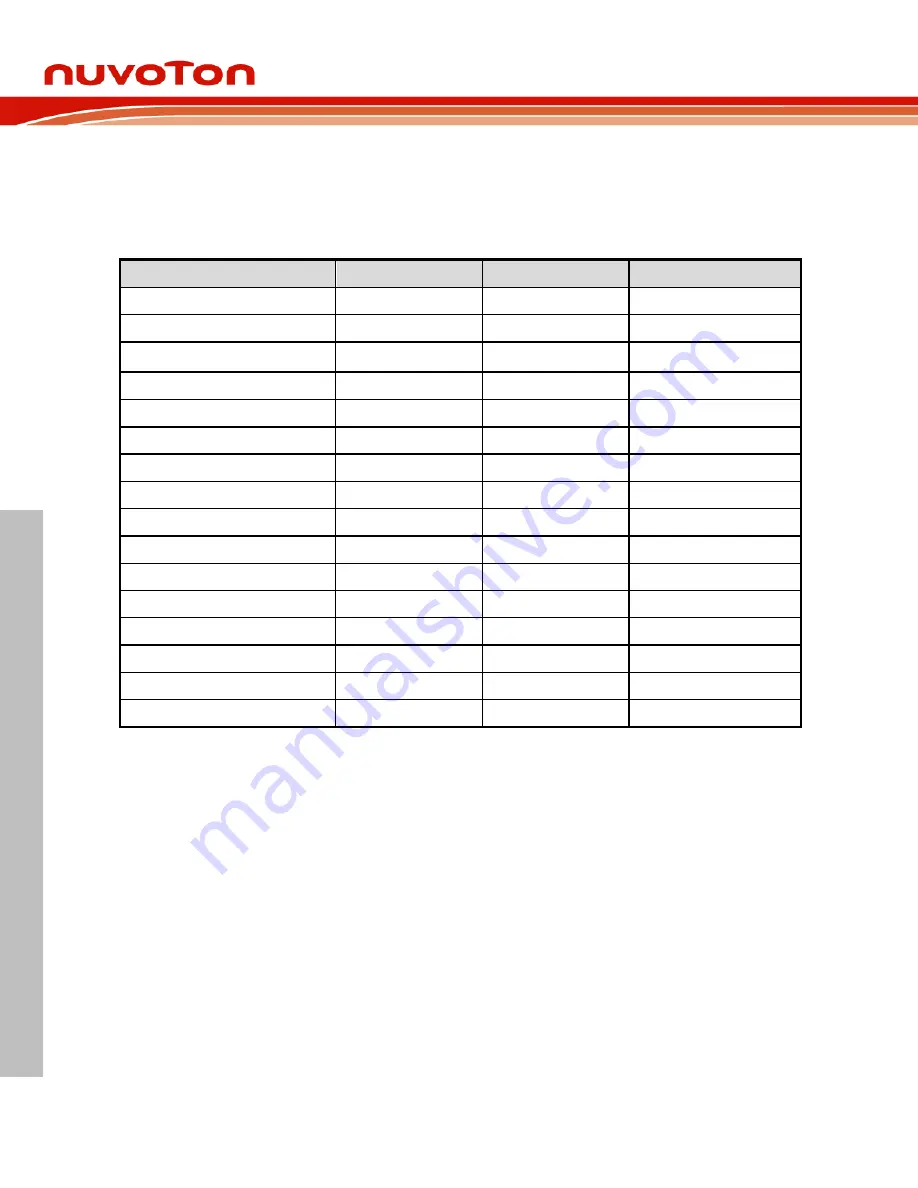

6.11.5.2 RTC Read/Write Enable

If RWENF(RTC_RWEN[16]) bit is read as 1, it means the RTC registers are read/write accessible.

When executing write RTC register command exceed 6 times within 1120 PCLK cycles, the

RTCBUSY(RTC_RWEN[24]) flag will be set 1 and RWENF(RTC_RWEN[16]) will be clear to 0. The

RTC control registers access attribute when RWENF is 1 and 0 are shown in Table 6.11.5-1.

Register

INIT[0] = 0

RWENF = 1

RWENF = 0 Or RTCBUSY=1

RTC_INIT

available

R/W

R/W

RTC_RWEN

available

R/W

R/W

RTC_FREQADJ

available

R/W

R

RTC_TIME

Not available

R/W

R

RTC_CAL

Not available

R/W

R

RTC_CLKFMT

Not available

R/W

R

RTC_WEEKDAY

Not available

R/W

R

RTC_TALM

Not available

R/W

R

RTC_CALM

Not available

R/W

R

RTC_LEAPYEAR

Not available

R

R

RTC_INTEN

available

R/W

R/W

RTC_INTSTS

available

R/W

R/W

RTC_TICK

Not available

R/W

R

RTC_TAMSK

Not available

R/W

R

RTC_CAMSK

Not available

R/W

R

RTC_LXTCTL

available

R/W

R/W

Table 6.11.5-1 RTC Read/Write Enable

6.11.5.3 Frequency Compensation

The RTC_FREQADJ register allows user to make digital compensation to a clock input. Please

follow the example and formula below to write the actual frequency of 32k crystal to RTC_FREQADJ

register. Following are the compensation examples for higher or lower than 32768 Hz.

Example 1:

Frequency counter measurement : 32773.65 Hz (> 32768 Hz)

FREQADJ = (32768 * 0x200000) / 32773.65 = 0x1FFE96

Example 2:

Frequency counter measurement : 32763.25 Hz (< 32768 Hz)

FREQADJ = (32768 * 0x200000) / 32763.25 = 0x200130

Note:

The value of RTC_FREQADJ register will be the default value (0x0020_0000) while the

compensation is not executed. User can utilize a frequency counter to measure RTC clock source

via clock output function in manufacturing. In the meanwhile, user can use clock output function to

check the result of RTC frequency compensation.