ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

56

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

Deep Power-down mode (DPD)

In Deep Power-down mode (DPD), all power supply is disabled except DPD control logic. The DPD

control logic controls Deep Power-down mode wake-up functions. After wake-up from Deep Power-

down mode (DPD), system resets and executes code from the beginning again. All peripheral

configurations return to default value and all SRAM data will be lost. The Deep Power-down mode

(DPD) wake-up sources include Wake-up Timer and Wake-up Pin (PA.15).

6.2.5

Power Modes Settings and Wake-up Sources

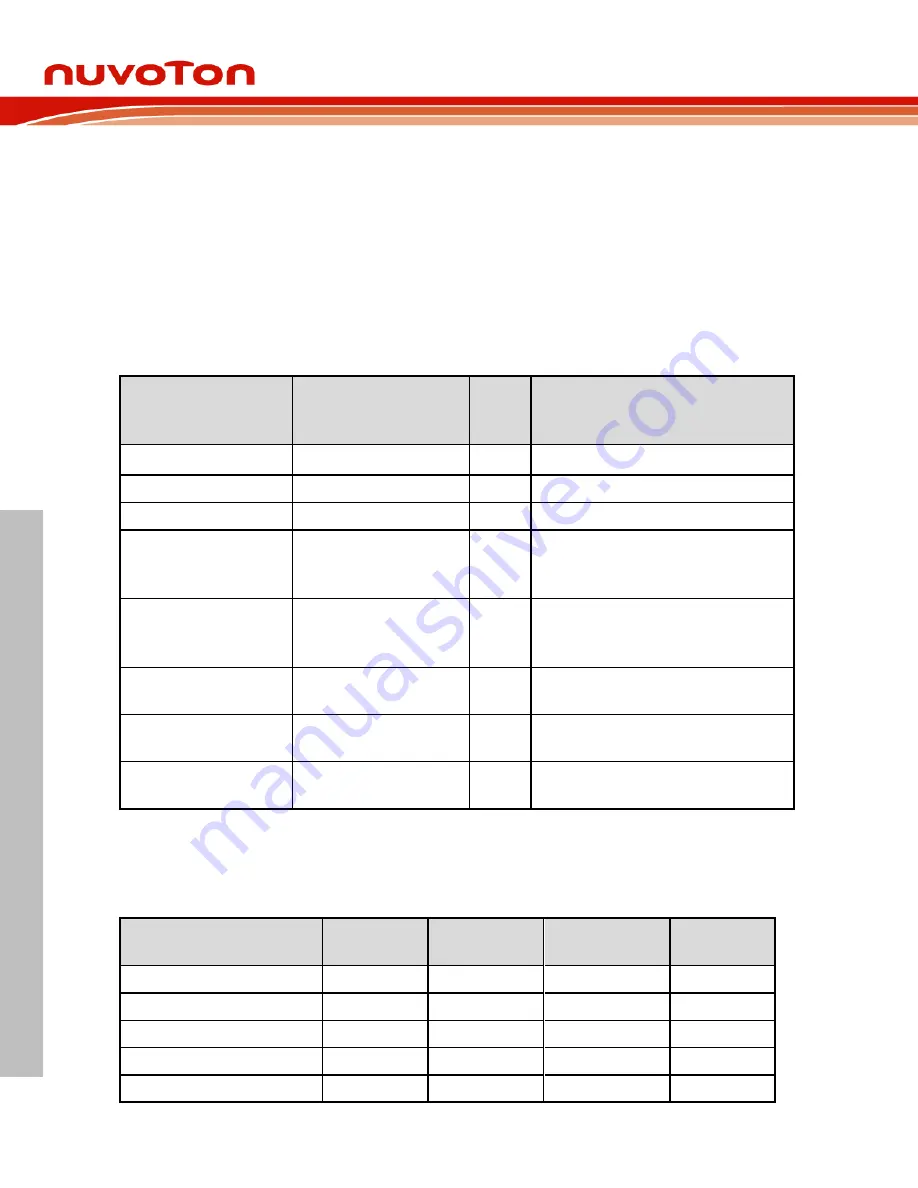

ISD94100 series is equipped with power management unit to support different power modes for

saving power. Table 6.2.5-1 lists all power mode at ISD94100 series.

Power Mode

CPU operating maximum

speed

(MHz)

LDO_CAP

(V)

Clock Disable

Normal mode

160

1.20

All clocks are disabled by control register.

Turbo mode

200

1.26

All clocks are disabled by control register.

Idle mode

CPU enter Sleep mode

1.20

Only CPU clock is disabled.

Power-down mode

(PD)

CPU enters Deep Sleep mode

1.20

Most clocks are disabled except LIRC/LXT, and

only RTC/WDT/Timer/UART peripheral clocks

still enable if their clock sources are selected as

LIRC/LXT.

Low leakage Power-down

mode

(LLPD)

CPU enters Deep Sleep mode

0.9

Most clocks are disabled except LIRC/LXT, and

only RTC/WDT/Timer/UART peripheral clocks

still enable if their clock sources are selected as

LIRC/LXT.

Standby Power-down mode 0

(SPD0)

Power off

Floating Only LIRC still enable for wake-up timer usage

Standby Power-down mode 1

(SPD1)

Power off

Floating Only LIRC still enable for wake-up timer usage

Deep Power-down mode

(DPD)

Power off

Floating Only LIRC still enable for wake-up timer usage

Table 6.2.5-1 Power Mode Table

There are different power mode entry settings. Each power mode has different entry setting and

leaving condition. Table 6.2.5-2 shows the enry setting for each power mode. When chip power-on,

chip is running at normal mode. User can enter each mode by configuring SLEEPDEEP (SCR[2]),

PDEN (CLK_PWRCT[7]) and PDMSEL (CLK_PMUCTL[2:0]) bits and then execute WFI instruction.

Register/Instruction

Mode

SLEEPDEEP

(SCR[2])

PDEN

(CLK_PWRCTL[7])

PDMSEL

(CLK_PMUCTL[2:0])

CPU Run WFI

Instruction

Normal mode

0

0

0

NO

Idle mode

0

0

0

YES

Power-down mode

1

1

0

YES

Low leakage Power-down mode

1

1

1

YES

Standby Power-down mode 0

1

1

4

YES