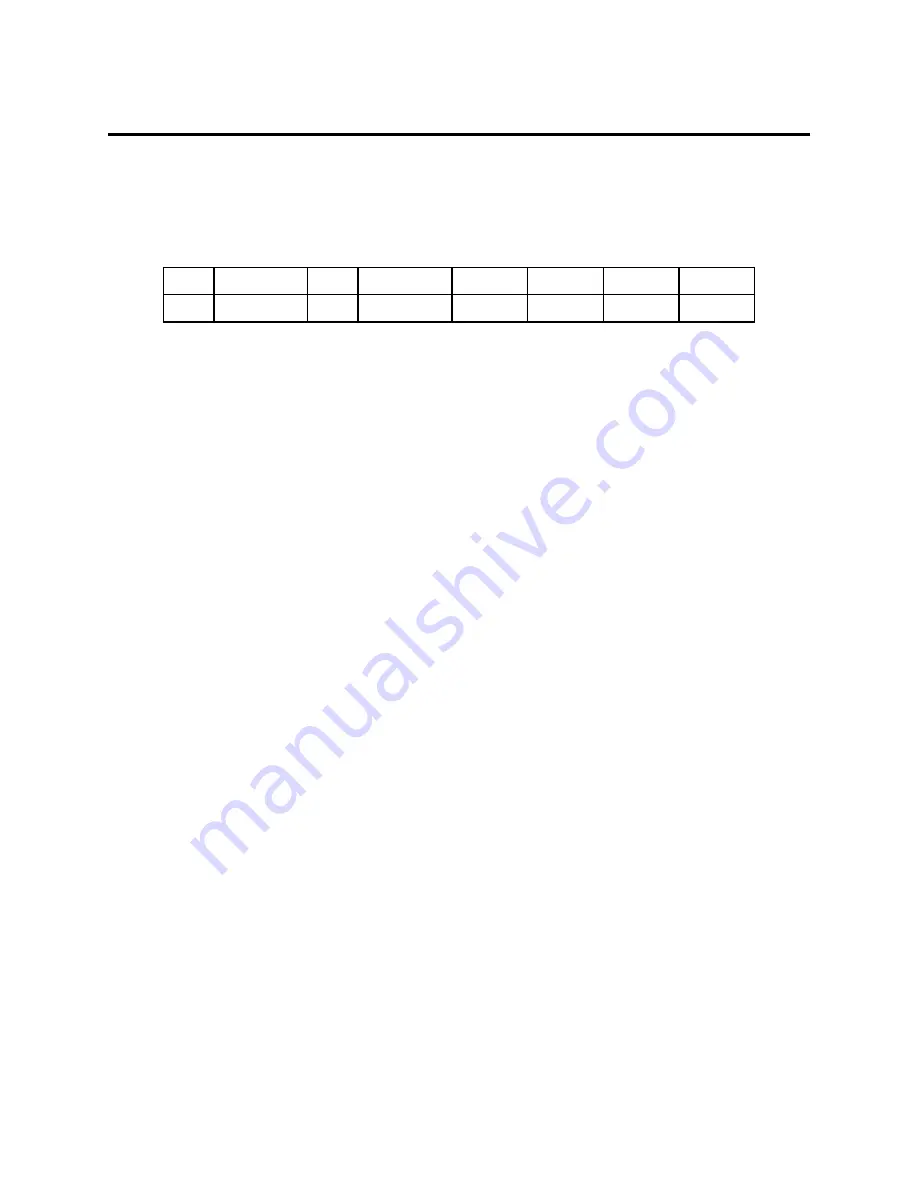

11 Communications Register

The Communications Register is used to set options pertaining to the clocks. The source

and type of clock to be transmitted or received can be specified. External synchronization can

also be controlled with this register. The address of the Communications Register is Base+4.

Table 9 details its bit definitions.

TXDEN

RXDEN

TCKEN

RCKEN

SW_SYNC

0

EXTSYNC

0

Bit 0

Bit 1

Bit 2

Bit 3

Bit 4

Bit 5

Bit 6

Bit 7

Table 9 --- Communications Register - Read/Write

Bit 7:

Reserved, always 0.

Bit 6:

EXTSYNC --- External Sync Enable:

If this bit is set (logic 1), software-controlled sync is disabled and the SCC's

SYNCA input is driven by the signal coming on pin 21 of the DB-25 connector.

If this bit is clear (logic 0), the SW_SYNC bit can be used to drive SYNCA.

Bit 5:

Reserved, always 0.

Bit 4:

SW_SYNC --- Software Sync On:

This bit is

used to drive the active-low SYNC input of the channel A receiver. The SYNC

signal is asserted when this bit is set (logic 1), and is deasserted when this bit is

clear (logic 0). This is useful in situations where it is necessary to receive

unformatted serial data, as it allows the SCC receiver to be manually placed into

sync under program control. This bit is ignored if bit 6 is set (logic 1).

44