R01UH0823EJ0100 Rev.1.00

Page 1377 of 1823

Jul 31, 2019

RX23W Group

38. Serial Peripheral Interface (RSPIa)

38.3.6

Communications Operating Mode

Full-duplex synchronous serial communications or transmit operations only can be selected by the communications

operating mode select bit (SPCR.TXMD). The SPDR access shown in

and

condition of access to the SPDR register, where W denotes a write cycle.

38.3.6.1

Full-Duplex Synchronous Serial Communications (SPCR.TXMD = 0)

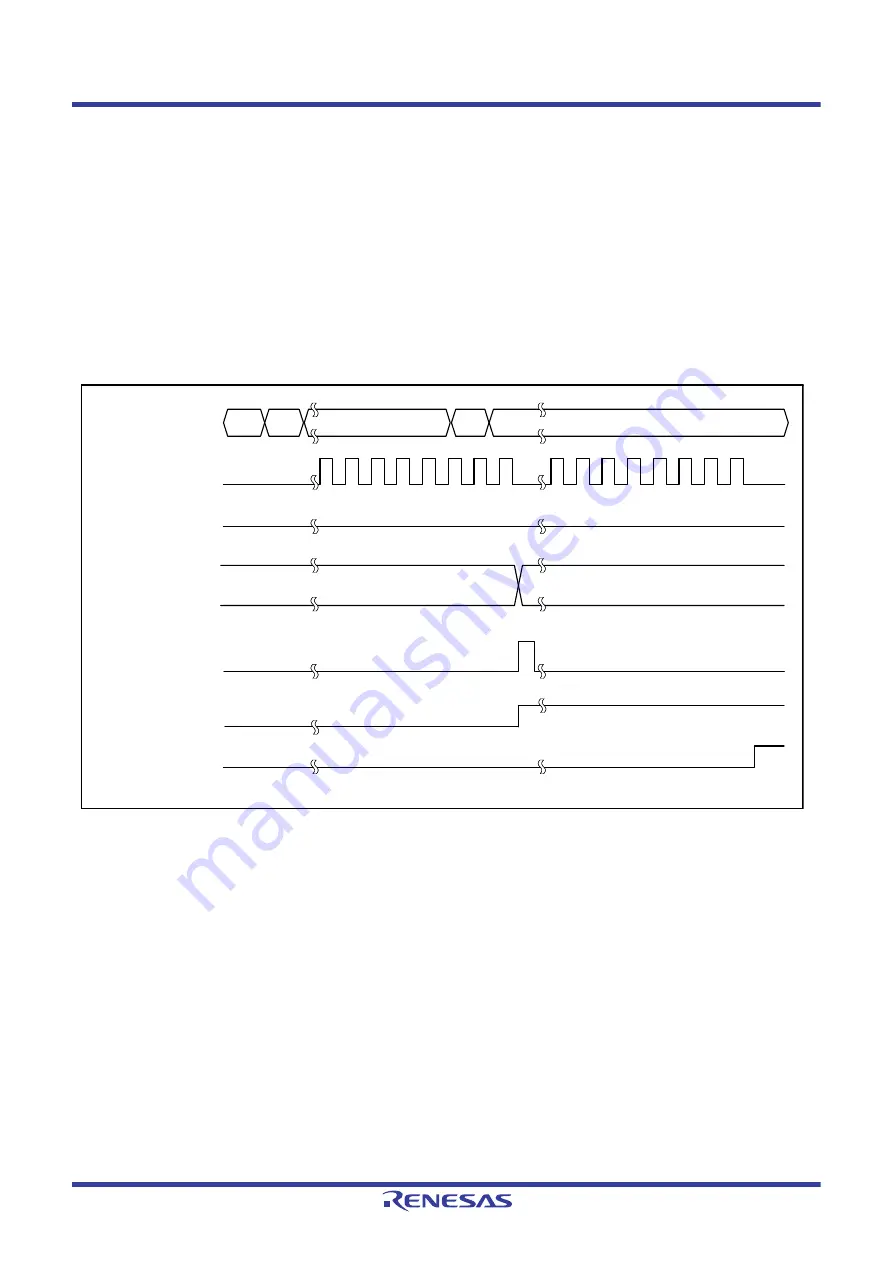

shows an example of operation when the communications operating mode select bit (SPCR.TXMD) is set

to 0. In the example in

, the RSPI performs an 8-bit serial transfer in which the SPDCR.SPFC[1:0] bits are

00b, the SPCMDm.CPHA bit is 1, and the SPCMDm.CPOL bit is 0. The numbers given under the RSPCKA waveform

represent the number of RSPCK cycles (i.e., the number of transferred bits).

Figure 38.24

Operation Example of SPCR.TXMD = 0

The operation of the flags at timings shown in steps (1) and (2) in the figure is described below.

(1) When a serial transfer ends with the receive buffer of SPDR empty, the RSPI generates a receive buffer full interrupt

request (SPRI) (sets the SPSR.SPRF flag to 1) and copies the received data in the shift register to the receive buffer.

(2) When a serial transfer ends with the receive buffer of SPDR holding data that was received in the previous serial

transfer, the RSPI sets the SPSR.OVRF flag to 1 and discards the received data in the shift register.

When full-duplex synchronous serial communications (SPCR.TXMD = 0) is selected, reception occurs simultaneously

with transmit operations. As such, the SPRF and OVRF flags in the SPSR register become 1 at the timing described in

(1) and (2), respectively, according to the state of the receive buffer.

W

W

SPDR access

OVRF

SPRI

8

7

6

5

4

3

2

1

8

7

6

5

4

3

2

1

(1)

(2)

TXMD

(TXMD = 0)

Empty

Full

Receive buffer status

SPRF

(CPHA = 1, CPOL = 0)

RSPCKA