R01UH0823EJ0100 Rev.1.00

Page 313 of 1823

Jul 31, 2019

RX23W Group

16. Buses

16.3.5

Bus Priority Control Register (BUSPRI)

Note 1. These bits can be written to only once while the DTC and DMAC are stopped. When they are written to more than one time, the

operation is not guaranteed.

BPRA[1:0] Bits (Memory Bus 1 (RAM) Priority Control)

These bits specify the priority order for memory bus 1 (RAM).

When the priority order is fixed, internal main bus 2 has priority over internal main bus 1.

When the priority order is toggled, a bus has a lower priority when the request of that bus is accepted.

BPRO[1:0] Bits (Memory Bus 2 (ROM) Priority Control)

These bits specify the priority order for memory bus 2 (ROM).

When the priority order is fixed, internal main bus 2 has priority over internal main bus 1.

When the priority order is toggled, a bus has a lower priority when the request of that bus is accepted.

BPIB[1:0] Bits (Internal Peripheral Bus 1 Priority Control)

These bits specify the priority order for internal peripheral bus 1.

When the priority order is fixed, internal main bus 2 has priority over internal main bus 1.

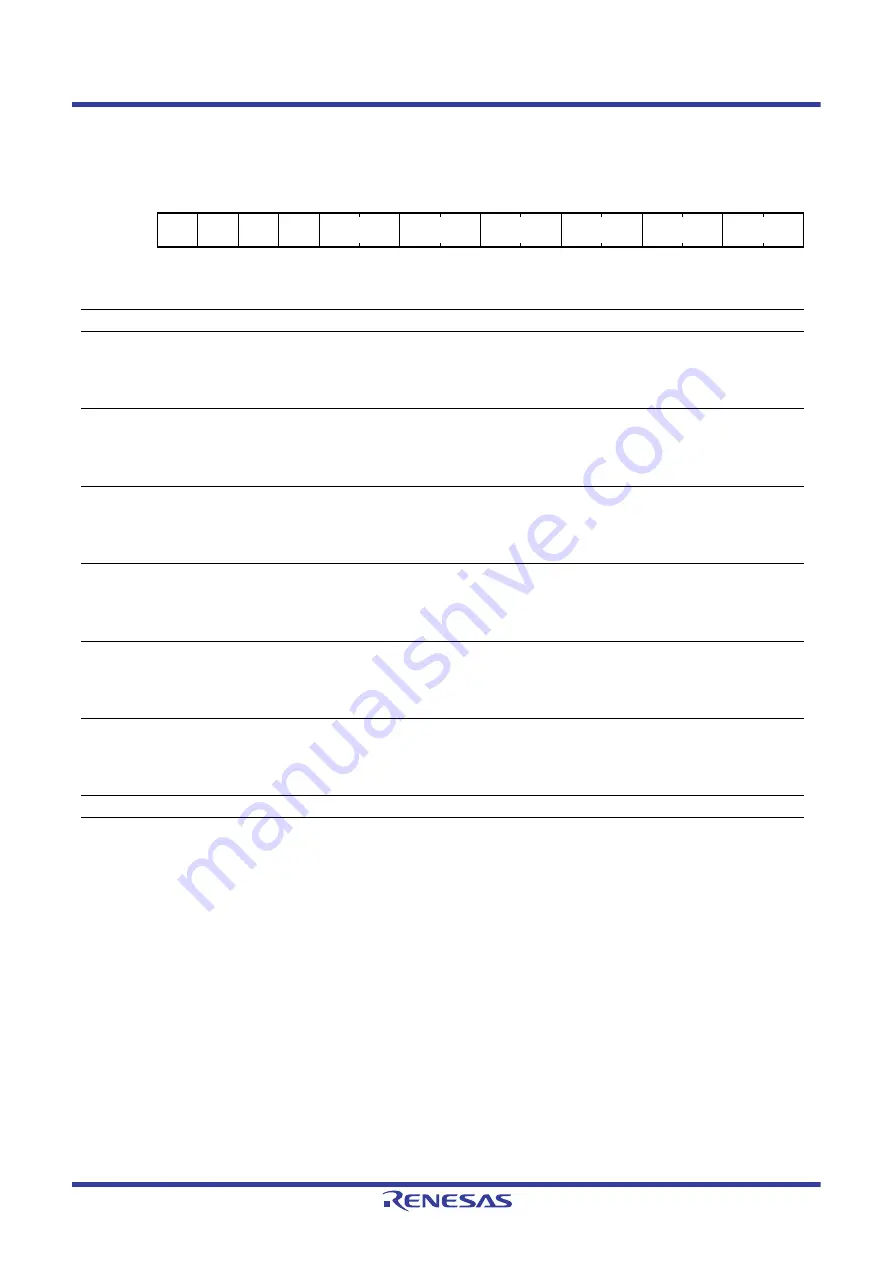

Address(es): 0008 1310h

b15

b14

b13

b12

b11

b10

b9

b8

b7

b6

b5

b4

b3

b2

b1

b0

—

—

—

—

BPFB[1:0]

BPHB[1:0]

BPGB[1:0]

BPIB[1:0]

BPRO[1:0]

BPRA[1:0]

Value after reset:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

Symbol

Bit Name

Description

R/W

b1, b0

Memory Bus 1 (RAM) Priority

Control

b1 b0

0 0: The order of priority is fixed.

0 1: The order of priority is toggled.

1 0: Setting prohibited

1 1: Setting prohibited

R(/W)

*

b3, b2

Memory Bus 2 (ROM) Priority

Control

b3 b2

0 0: The order of priority is fixed.

0 1: The order of priority is toggled.

1 0: Setting prohibited

1 1: Setting prohibited

R(/W)

*

b5, b4

Internal Peripheral Bus 1 Priority

Control

b5 b4

0 0: The order of priority is fixed.

0 1: The order of priority is toggled.

1 0: Setting prohibited

1 1: Setting prohibited

R(/W)

*

b7, b6

Internal Peripheral Bus 2 and 3

Priority Control

b7 b6

0 0: The order of priority is fixed.

0 1: The order of priority is toggled.

1 0: Setting prohibited

1 1: Setting prohibited

R(/W)

*

b9, b8

Internal Peripheral Bus 4 Priority

Control

b9 b8

0 0: The order of priority is fixed.

0 1: The order of priority is toggled.

1 0: Setting prohibited

1 1: Setting prohibited

R(/W)

*

b11, b10

Internal Peripheral Bus 6 Priority

Control

b11 b10

0 0: The order of priority is fixed.

0 1: The order of priority is toggled.

1 0: Setting prohibited

1 1: Setting prohibited

R(/W)

*

b15, b12

—

Reserved

These bits are read as 0. The write value should be 0.

R/W