R01UH0823EJ0100 Rev.1.00

Page 922 of 1823

Jul 31, 2019

RX23W Group

32. USB 2.0 Host/Function Module (USBc)

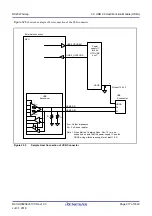

shows the interrupts generated in the USB0.

Table 32.13

USB Interrupts

32.3.3

Interrupt Descriptions

32.3.3.1

BRDY Interrupt

The BRDY interrupt is generated when either of the host controller or function controller is selected. The following

shows the conditions under which the USB sets 1 to a corresponding bit in the BRDYSTS register. Under this condition,

the USB generates a BRDY interrupt if software has set 1 to the BRDYENB.PIPEnBRDYE bit that corresponds to the

pipe and 1 to the INTENB0.BRDYE bit.

The conditions for generating and clearing the BRDY interrupt depend on the settings of the SOFCFG.BRDYM bit and

PIPECFG.BFRE bit for each pipe as described below.

(1) When the SOFCFG.BRDYM Bit = 0 and the PIPECFG.BFRE Bit = 0

With these settings, the BRDY interrupt indicates that the FIFO port is accessible.

On any of the following conditions, the USB generates an internal BRDY interrupt request trigger and sets 1 to the

BRDYSTS.PIPEnBRDY flag corresponding to the pertinent pipe.

(a) For the pipe in the transmitting direction:

When the DIR bit is changed from 0 to 1 by software.

When packet transmission is completed using the pertinent pipe while write-access from the CPU to the FIFO

buffer for the pertinent pipe is disabled (when the BSTS flag is read as 0).

When one FIFO buffer is empty on completion of writing data to the other FIFO buffer in double buffer mode.

No request trigger is generated until completion of writing data to the currently-written FIFO buffer even if

transmission to the other FIFO buffer is completed.

When the hardware flushes the buffer of the pipe for isochronous transfers.

When 1 is written to the PIPEnCTR.ACLRM bit, which causes the FIFO buffer to make transition from the write-

disabled to write-enabled state.

No request trigger is generated for the DCP (that is, during data transmission for control transfers).

Interrupt

Name

Interrupt Status Flag

DTC

Activation

DMAC

Activation

D0FIFO

DMA/DTC transfer request 0

Possible

Possible

D1FIFO

DMA/DTC transfer request 1

Possible

Possible

USBI

VBUS interrupt, resume interrupt, frame number update interrupt, device state

transition interrupt, control transfer stage transition interrupt, buffer empty interrupt,

buffer not ready interrupt, buffer ready interrupt, overcurrent input change interrupt,

bus change interrupt, disconnection detection during full-speed operation, device

connection detection, EOF error detection, normal setup operation, setup error, and

portable device detection interrupt

Not possible

Not possible

USBR

VBUS interrupt, resume interrupt, overcurrent input change interrupt, bus change

interrupt, and portable device detection interrupt

Not possible

Not possible