System Address Space

A–35

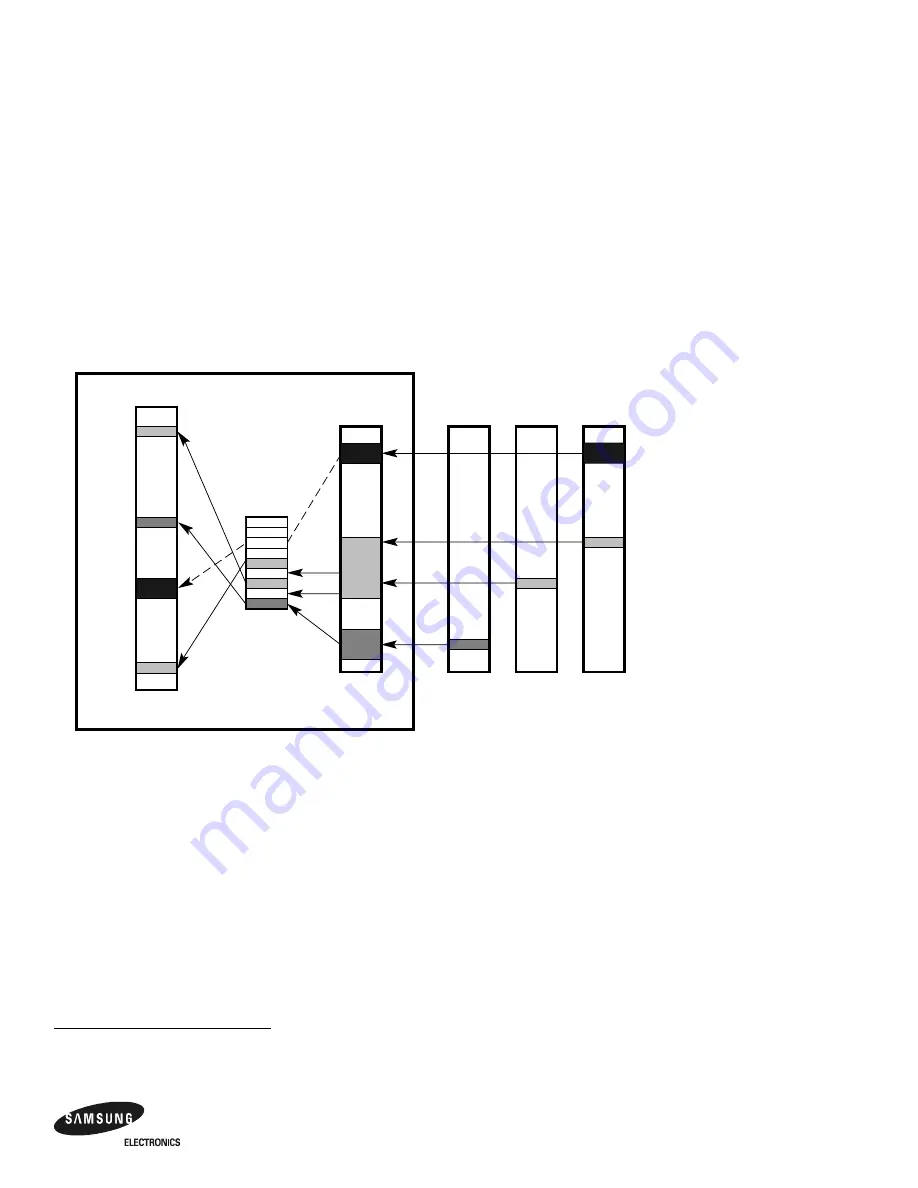

PCI to Physical Memory Address

Figure 1–17 PCI DMA Addressing Example

Figure 1–18 shows the PCI window logic. The comparison logic associated with

ad<63:32> is only used for DAC

1

mode; and only if enabled by a bit in the

window base register for window 3. This logic is only applicable to window 3. The

remaining windows only recognize 32-bit PCI addresses (that is, SAC

2

cycles).

For a hit to occur in a DAC address, ad<63:40> must be zero, ad<39:32> must

match the window DAC base register, and ad<31:20> must also have a compare hit.

This scheme allows a naturally aligned, 1MB–4GB PCI window to be placed any-

where in the first 1TB of a 64-bit PCI address. When an address match occurs with a

PCI target window, the 21174 translates the 32-bit PCI address to addr_h<33:0>.

1 Dual-address cycle (DAC) — only issued if <63:32> are nonzero for a 64-bit address.

2 Single-address cycle (SAC) — all 32-bit addresses. A PCI device must use SAC if

<63:32> equals 0.

LJ-05402.AI4

21164 Memory

Space (8GB)

Scatter-Gather

Map

PCI Device's DMA

Memory Space

PCI Memory

Space (4GB)

8KB

Page

PCI

Device 0

PCI

Device 1

PCI

Device 2

21164 System